# JP8101791

**Publication Title:**

VARIABLE-LENGTH BIT DATA PROCESSING CIRCUIT AND METHOD

# Abstract:

A variable bit-length code processing circuit includes first, second and third registers (12, 20, 22) each of which is of 1 word, and memory data is loaded to the first register (12), and a variable bit-length code is withdrawn from the third register (22). The second register (20) and third register (22) are coupled to a barrel shifter (16) which barrel-shifts data of 2 words according to a barrel shift amount which is applied by a subtracter (30) on the basis of the number of the valid bits and the number of the remaining bits.

-----

Data supplied from the esp@cenet database - http://ep.espacenet.com

# (19)日本国特許庁(JP) (12) 公開特許公報(A)

(11)特許出願公開番号

# 特開平8-101791

(43)公開日 平成8年(1996)4月16日

| (51) Int.Cl. <sup>6</sup> G 0 6 F 12/04 // H 0 3 M 7/40 H 0 4 N 1/41 7/24 | 識別記号<br>5 4 0 B<br>Z | 庁内整理番号<br>7623-5B<br>9382-5K | FΙ                  | 技術表示箇所                       |

|---------------------------------------------------------------------------|----------------------|------------------------------|---------------------|------------------------------|

| -,                                                                        |                      |                              | H 0 4 N             | 7/ 13 Z                      |

|                                                                           |                      |                              | 審査請求                | 未請求 請求項の数6 OL (全18頁)         |

| (21)出願番号                                                                  | 特願平6-236971          |                              | (71)出願人             | 394014250                    |

|                                                                           |                      |                              |                     | 株式会社クリエイティブ・デザイン             |

| (22)出願日                                                                   | 平成6年(1994)9月         | ₹30日                         |                     | 兵庫県川西市中央町3番6号                |

|                                                                           |                      |                              | (71)出願人             |                              |

|                                                                           |                      |                              |                     | 任天堂株式会社                      |

|                                                                           |                      |                              | (70) ₹%¤¤± <b>±</b> | 京都府京都市東山区福稲上高松町60番地          |

|                                                                           |                      |                              | (72)発明者             | 高橋 豊文<br>兵庫県川西市中央町3番6号 株式会社ク |

|                                                                           |                      |                              |                     | リエイティブ・デザイン内                 |

|                                                                           |                      |                              | (72)発明者             |                              |

|                                                                           |                      |                              |                     | 兵庫県川西市中央町3番6号 株式会社ク          |

|                                                                           |                      |                              |                     | リエイティブ・デザイン内                 |

|                                                                           |                      |                              | (74)代理人             | 弁理士 山田 義人                    |

|                                                                           |                      |                              |                     | 最終頁に続く                       |

# (54) 【発明の名称】 可変長ビットデータ処理回路および方法

### (57)【要約】

【構成】 それぞれが1ワードである第1, 第2および 第3レジスタ12,20および22を設け、第1レジス タ12にメモリからのデータがロードされ、第3レジス タ22から可変長ビットデータが取り出される。第2レ ジスタ20および第3レジスタ22はバレルシフタ16 に結合され、バレルシフタ16は減算器30から与えら れる有効ビット数および残ビット数に基づくバレルシフ ト量データに従って2ワードのデータをバレルシフトす る。

【効果】 合計3ワードのレジスタおよびバレルシフタ を用い、最大2回のバレルシフト動作で第3レジスタか ら可変長ビットの有効データが取り出されるので、回路 構成および処理動作を簡略化できる。

### 【特許請求の範囲】

【請求項1】ビット並列に与えられるデータを保持する 1ワードの第1レジスタ、

前記第1レジスタからのデータをビット並列に受ける1 ワードの第2レジスタ、

可変長ビットデータが取り出される1ワードの第3レジ スタ、

有効ビット数と前記第2レジスタに保持されたデータの 残ビット数とを比較して前記有効ビット数が前記残ビット数より大きいとき第1信号を出力する比較手段、

前記比較手段から前記第1信号が出力されたとき、前記第2レジスタおよび前記第3レジスタから前記残ビット数だけバレルシフトしたデータを前記第3レジスタへロードする第1バレルシフト手段、

前記比較手段から前記第1信号が出力されたとき、前記第1レジスタのデータを前記第2レジスタにビット並列でロードするロード手段、および前記ロード手段によって前記第2レジスタに前記第1レジスタのデータをロードした後、前記有効ビット数と前記残ビット数との差のビット数だけバレルシフトした前記第2レジスタおよびが記第3レジスタのデータを前記第2レジスタおよび前記第3レジスタにロードする第2バレルシフト手段を備える、可変長ビットデータ処理回路。

【請求項2】前記比較手段は前記有効ビット数と前記残 ビット数とが等しいとき第2の信号を出力し、

前記比較手段から前記第2信号が出力されたとき、前記 残ビット数だけバレルシフトした前記第2レジスタおよ び前記第3レジスタのデータを前記第3レジスタにロー ドする第3バレルシフト手段、および前記比較手段から 前記第2信号が出力されたとき、前記第1レジスタのデ 30 ータを前記第2レジスタにビット並列でロードするロー ド手段を備える、請求項1記載の可変長ビットデータ処 理回路。

【請求項3】前記比較手段は前記残ビット数が前記有効 ビット数より大きいとき第3信号を出力し、

前記比較手段から前記第3信号が出力されたとき、前記第2レジスタおよび前記第3レジスタのデータを前記有効ビット数だけバレルシフトして前記第2レジスタおよび前記第3レジスタにロードする第4バレルシフト手段を備える、請求項1または2記載の可変長ビットデータ 40 処理回路。

【請求項4】ビット並列に与えられるデータを保持する 1ワードの第1レジスタ、前記第1レジスタからのデー タをビット並列に受ける1ワードの第2レジスタ、およ び可変長ビットデータが取り出される1ワードの第3レ ジスタを備える可変長ビットデータ処理回路における処 理方法であって、

有効ビット数が前記第2レジスタに保持されたデータの ビットをシフトレジスタ(11)によって押し出した分だけ 残ビット数より大きいとき、(a) 前記第2レジスタおよ シフトレジスタ(12)によってシフトしかつビット単位に び前記第3レジスタから前記残ビット数だけバレルシフ 50 シフトレジスタ(11)に書き込むようにしているため、従

トしたデータを前記第3レジスタへロードし、(b) 前記第1レジスタのデータを前記第3レジスタへロードし、(b) 前記

第1レジスタのデータを前記第2レジスタにビット並列でロードし、そして(c) 前記第2レジスタおよび前記第3レジスタのデータを前記有効ビット数と前記残ビット数との差のビット数だけバレルシフトして前記第2レジ

スタおよび前記第3レジスタにロードする、処理方法。

2

【請求項5】前記有効ビット数と前記残ビット数とが等しいとき、(d) 前記残ビット数だけバレルシフトした前記第2レジスタおよび前記第3レジスタのデータを前記10 第2レジスタおよび前記第3レジスタにロードし、そして(e) 前記第1レジスタのデータを前記第2レジスタにビット並列でロードする、請求項4記載の処理方法。

【請求項6】前記残ビット数が前記有効ビット数より大きいとき、(f) 前記第2レジスタおよび前記第3レジスタのデータを前記有効ビット数だけバレルシフトして前記第2レジスタおよび前記第3レジスタにロードする、請求項4または5記載の処理方法。

#### 【発明の詳細な説明】

[0001]

【産業上の利用分野】この発明は可変長ビットデータ処理回路および方法に関し、特にたとえば、画像や音声の圧縮データのように、メモリに効率よく(余白なしに)格納されている可変長ビットデータを処理する、処理回路および方法に関する。

[0002]

【従来の技術】この種の可変長ビットデータ処理回路の一例が、平成4年(1992)9月2日付で出願公開された特開平4-245778号公報に開示されている。この従来技術は、入力符号データを保持する1ワードのシフトレジスタ(11)と、そのシフトレジスタ(11)からビット並列に転送されるデータを保持する3ワードのシフトレジスタ(12)とを含み、シフト/転送制御部(30)がシフトレジスタ(12)内のデータ余白部分を充足させる分だけシフトレジスタ(11)内のデータを切り出して転送するものである。

#### [0003]

【発明が解決しようとする課題】従来技術では、不要になった前回のデータをシフトレジスタ(12)で直列シフトして排出するようにしているため、合計4ワード分のシフトレジスタと、それらのシフト動作を制御するためのシフト/転送制御とが必要となる。シフト/転送制御の詳細については開示されていないが、シフト回数を計数するカウンタ、シフトクロックの制御回路、シフトレジスタ11からシフトレジスタ12への任意のビット数のデータを並列転送する転送制御回路、およびシーケンサ等が必要となり、回路規模が大きくなってしまう。さらに、次のデータとビットストリームでつなぐために余白ビットをシフトレジスタ(11)によって押し出した分だけシフトレジスタ(12)によってシフトしかつビット単位にシフトレジスタ(11)にままされた。とれているためにオールによった。

来技術では、処理ステップが多くなり、データを取り出 す時間が長くかかってしまうという問題点があった。

【0004】それゆえに、この発明の主たる目的は、簡単な回路でかつより高速に、可変長ビットデータを取り出すことができる、データ処理回路および方法を提供することである。

# [0005]

【課題を解決するための手段】この発明は、ビット並列 に与えられるデータを保持する1ワードの第1レジス タ、第1レジスタからのデータをビット並列に受ける1 ワードの第2レジスタ、可変長ビットデータが取り出さ れる1ワードの第3レジスタ、有効ビット数と第2レジ スタに保持されたデータの残ビット数とを比較して有効 ビット数が残ビット数より大きいとき第1信号を出力す る比較手段、比較手段から第1信号が出力されたとき、 第2レジスタおよび第3レジスタから残ビット数だけバ レルシフトしたデータを第3レジスタへロードする第1 バレルシフト手段、比較手段から第1信号が出力された とき、第1レジスタのデータを第2レジスタにビット並 列でロードするロード手段、およびロード手段によって 20 第2レジスタに第1レジスタのデータをロードした後、 有効ビット数と残ビット数との差のビット数だけバレル シフトした第2レジスタおよび第3レジスタのデータを 第2レジスタおよび第3レジスタにロードする第2バレ ルシフト手段を備える、可変長ビットデータ処理回路で ある。

【0006】この発明は、また、ビット並列に与えられるデータを保持する1ワードの第1レジスタ、第1レジスタからのデータをビット並列に受ける1ワードの第2レジスタ、および可変長ビットデータが取り出される1ワードの第3レジスタを備える可変長ビットデータ処理回路における処理方法であって、有効ビット数が第2レジスタに保持されたデータの残ビット数より大きいとき、(a)第2レジスタおよび第3レジスタから残ビット数だけバレルシフトしたデータを第3レジスタへロードし、(b)第1レジスタのデータを第2レジスタにビット並列でロードし、そして(c)第2レジスタおよび第3レジスタのデータを有効ビット数と残ビット数との差のビット数だけバレルシフトして第2レジスタおよび第3レジスタにロードする、処理方法である。

#### [0007]

【作用】たとえばメモリから読み出された1ワードのデータが第1レジスタにビット並列にロードされる。この 第1レジスタのデータが第2レジスタにビット並列にロ ド (16ビット)のレジスタであり、この第2レジスタ 20は1ワードされ、第2レジスタのデータが第1バレルシフト手 段によってたとえば16ビットシフトされて第3レジスタから、可変長ビットデータが取り出される。たとえば減算器からなる比較手段 において、たとえば10 アリンスタに関する。 第10 アリンスタ 11 を 12 と 13 と 14 において、たとえば15 と 15 において、たとえば 15 と 15 において、たとえば 15 と 15 において、たとえば 15 と 15

4 その減算結果が角になった

ら減算する。そして、その減算結果が負になったとき、減算器からボロー信号(第1信号)が出力される。このボロー信号が出力されたとき、バレルシフタが動作し、第2レジスタおよび第3レジスタのデータを残ビット数だけバレルシフトしてそれを第3レジスタにロードする。このとき、第1バレルシフト手段のバレルシフトによってはみ出したデータは失われ、使用されない。それとともに、第1レジスタのデータが第2レジスタのデータが第3レジスタのデータが第3レジスタのデータが第3レジスタのデータとともに(有効ビット数一残ビット数)だけ第2バレル手段によってバレルシフトされて第2レジスタおよび第3レジスタにロードされる。第2バレルシフト手段のバレルシフトによって空きが生じた第2レジスタの空白部には「0」が書き込まれる。

## [0008]

【発明の効果】この発明によれば、合計3ワードのラッチと、バレルシフト手段を構成するための複数のセレクタや減算器があればよく、従来技術に比べて、回路構成が簡単になるとともに、多くても2ステップのバレルシフト動作で有効データがセットできるので、処理時間が短縮され、データ処理が一層高速化される。

【0009】この発明の上述の目的,その他の目的,特 徴および利点は、図面を参照して行う以下の実施例の詳 細な説明から一層明らかとなろう。

#### [0010]

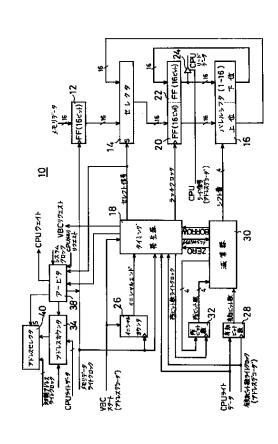

【実施例】図1に示す可変長ビットデータ処理回路10 は、メモリ(図示せず)から出力される可変長ビットデ ータを処理するための回路であって、そのメモリからの 1ワードのメモリデータをビット並列に受ける1ワード (16ビット)の第1レジスタ12を含む。この第1レ ジスタ12のデータは、ビット並列にセレクタ14に与 えられる。セレクタ14は2入力(各16ビット)のい ずれかを選択して出力するものであって、一方入力とし て上述の第1レジスタ12からの16ビットが、他方入 カとしてバレルシフタ16の上位16ビットが与えられ る。セレクタ14は、タイミング発生器18からの 「0」または「1」のセレクト信号に応じて、第1レジ スタ12からのデータまたはバレルシフタ16からのデ ータを選択的に、第2レジスタ20にビット並列にロー ドする。したがって、このセレクタ14は、第1ないし 第4バレルシフト手段の一部を構成するとともに、第1 レジスタ12のデータを第2レジスタ20にロードする ロード手段として機能する。第2レジスタ20は1ワー ド(16ビット)のレジスタであり、この第2レジスタ 20のデータはビット並列にバレルシフタ16に与えら れる。第3レジスタ22もまた1ワード(16ビット) のレジスタである。なお、便宜上、第2レジスタ20お よび第3レジスタ22は個別のものとして説明したが、 実際には、2ワード(32ビット)の1つのレジスタな

40

タがバレルシフタ16の上位16ビットに与えられ、第 3レジスタ22のデータがバレルシフタ16の下位16 ビットに与えられる。バレルシフタ16は、第2レジス タ20および第3レジスタ22のそれぞれの16ビット 並列データを1つの32ビットデータとして右方向にバ レルシフトする。バレルシフトしたデータの上位16ビ ットは上述のようにセレクタ14に与えられるが、バレ ルシフトしたデータの下位16ビットは第3レジスタ2 2にビット並列で与えられる。したがって、このバレル シフタ16が第1ないし第4バレルシフト手段の一部を 構成することは明らかである。その結果、第3レジスタ 22のデータが、CPU (図示せず) によって有効デー タとして3状態ゲート24から取り出される。

【0011】ここで、バレルシフトについて説明する。 通常のシフトレジスタを用いたデータシフトでは、1回 与えられるクロックに応答してデータが1ビット分だけ 右または左にシフトされる。たとえば、データを5ビッ トシフトする場合は、5つのクロックに応答してデータ が右または左に5ビットシフトされる。これに対して、 に応答して、データが1度に複数ビット右または左にシ フトされる。1回のクロックでシフトするビット数は、 減算器30 (後述) から与えられるシフト量により決定 される。

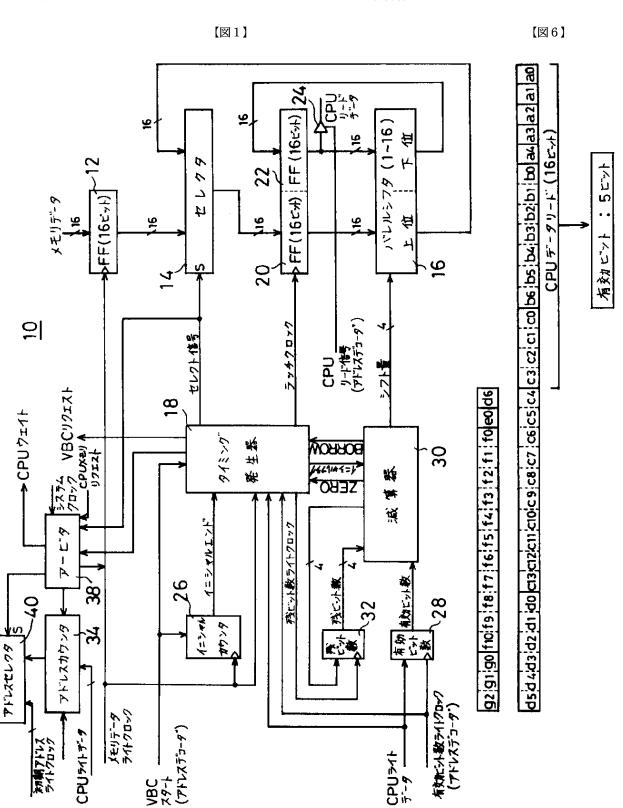

【0012】このようなバレルシフトを行うために、こ の実施例のバレルシフタ16は、図2に示すように、3 2個のセレクタSBL0-SBL31を用いて構成することができ る。バレルシフタ16には、第3レジスタ22からの1 6 ビットの並列データb16-b31 と第2レジスタ20から の16ビットの並列データb0-b15の計32ビットのデー 夕が与えられる。この32ビットのデータの各ビット を、下位から上位にかけてそれぞれb0-b31とする。

【0013】一方、先に述べたように、バレルシフタ1 6は、最大で16ビットのバレルシフトを行うことがで きる。このバレルシフトは、セレクタSBLO-SBL31によっ て実現される。以下に、各セレクタSBL0-SBL31の動作に ついて説明する。バレルシフタ16の最下位ビットの出 力を決定するセレクタSBLOは、ビットb1-b16の中から1 ビットを選択して出力する16-1セレクタ(16ビッ トの中から任意の1ビットを選択して出力するセレク タ)であり、選択するビットは減算器30(図1)から 与えられるシフト量に応答して決定される。同様に、セ レクタSBL1, SBL2, SBL3, …SBL15 は、それぞれ、ビッ トb2-b17, b3-b18, b4-b19, …b16-b31 の中から、減算 器30から与えられるシフト量に応答して、1ビットを 選択して出力する16-1セレクタである。

【0014】一方、セレクタSBL16-SBL31 の各々は、セ レクタSBL0-SBL15に用いたような16-1セレクタによ って構成することができない。なぜならば、セレクタSB L16は、ビットb17-b32 の中から 1 ビットを選択して出 50 クを受け、それに応じてインクリメントされる。タイミ

6 力することができないからである。その理由は、バレル シフタ16には、32ビットb0-b31のデータしか与えら れておらず、バレルシフタ16に与えられていないビッ トb32 を選択することはできないからである。そこで、 セレクタSBL16 は、減算器30から与えられるシフト量 によって16ビットのバレルシフトを行うよう指示され た場合は、ビットb32 に代えて「O」を出力する。すな わち、セレクタSBL16 は、ビットb17-b31 または「O」 の中から1ビットを選択して出力する16-1セレクタ である。また、セレクタSBL17 は、バレルシフタ16に ビットb32 およびb33 が与えられていないため、ビット b18-b33 の中から1ビットを選択して出力することがで きず、したがって、減算器30によって15ビット以上 のバレルシフトを行うよう指示された場合、すなわち、 ビットb32 あるいはb33 を選択するよう指示された場合 は、「0」を出力する。換言すれば、セレクタSBL17 は、ビットb18-b31 または「O」の中から1ビットを選 択して出力する15-1セレクタである。同様に、セレ クタSBL18, SBL19, SBL20, …SBL30は、それぞれ、 ここでいうバレルシフトを用いた場合、1つのクロック 20 ビットb19-b31または「0」, ビットb20-b31 または 「0」, ビットb21-b31 または「0」, …ビットb31 ま たは「0」の中から1ビットを選択して出力する14-1セレクタ, 13-1セレクタ, 12-1セレクタ, … 2-1セレクタである。そして、セレクタSBL31 は、シ フト量の値によらず「0」しか出力しない1-1セレク タであり、セレクタSBL31 の出力は「0」に固定されて

> 【0015】このようにして、バレルシフタ16は、減 算器30(図1)によって指示されたシフト量に応じ て、第2レジスタ20および第3レジスタ22から与え られる32ビットb0-b31または「0」を選択し、結果的 に、所要のビット数だけバレルシフトし、そのバレルシ フトの結果、はみ出したビットは失われ、空白となった ビットには「0」が書き込まれる。

【0016】なお、第1レジスタ12には、メモリ(図 示せず) からのメモリデータが、メモリデータライトク ロック(後述)に応じてロードされ、セレクタ14から のデータはタイミング発生器18から出力されるラッチ クロックに応じて第2レジスタ20にロードされる。そ して、3状態ゲート24はアドレスデコーダ(図示せ ず) から出力される CPUリード信号によって制御され る。すなわち、このCPUリード信号が「1」のとき3 状態ゲート24からCPUリードデータが取り出され る。上述のアドレスデコーダは、可変長ビットデータ (VBC: Variable Bit-length Code) の処理のスター トを示すVBCスタート信号を出力し、このVBCスタ ート信号が、上述のタイミング発生器18に与えられる とともに、イニシャルカウンタ26に与えられる。イニ シャルカウンタ26はまた、メモリデータライトクロッ

いる。

ング発生器18は、VBCスタート信号に応じてイネーブルされ、VBCリクエスト信号を発生する。このVBCリクエスト信号は、メモリデータライトクロックに同期して発生される。

【0017】CPU(図示せず)からのCPUライトデータが有効ビット数レジスタ28に与えられるとともに、タイミング発生器18に与えられる。有効ビット数データは、たとえば4ビットで与えられ、バレルシフト量を決定するために用いられる。有効ビット数データが「0000」のとき「16」の有効ビット数を表し、有効ビット数データが「0001」のとき「1」の有効ビット数を表し、有効ビット数データが「0010」のとき「2」の有効ビット数で表し、以下同様に、有効ビット数データが「1111」のとき「15」の有効ビット数データが「1111」のとき「15」の有効ビット数データが「1111」のとき「15」の有効ビット数データが「1111」のとき「15」の有効ビット数データが「1111」のとき「15」の有効ビット数データが「1111」のとき「15」の有効ビット数に要素す。また、アドレスデコーダ(図示せず)からの有効ビット数ライトクロックが有効ビット数レジスタ28に与えられるとともに、タイミング発生器18に与えられる。

【0018】有効ビット数レジスタ28にロードされた 有効ビット数のデータは減算器30の一方入力に与えら 20 れる。減算器30の他方入力には、残ビット数レジスタ 32から出力される残ビット数のデータが与えられる。 すなわち、減算器30は「残ビット数ー有効ビット数」 の減算を実行するのであるから、第2レジスタ20の残 ビット数を自身で知ることができる。したがって、減算 器30から残ビット数データが出力され、タイミング発 生器18から残ビット数ライトクロックが残ビット数レ ジスタ32に与えられることによって、残ビット数レジ スタ32に残ビット数データが保持される。このように して、減算器30は「残ビット数ー有効ビット数」の演 30 算を行い、その減算結果を新たな残ビット数データとし て出力するとともに、後者が前者よりも大きいとき、

「1」のボロー信号(第1信号)を出力し、前者と後者とが等しいとき「1」のゼロ信号(第2信号)を出力する。したがって、ボロー信号およびゼロ信号がともに「0」とき、減算器30からは第3信号が出力されたことになる。ボロー信号およびゼロ信号は、ともに、タイミング発生器18では、ボロー信号やゼロ信号に応じて、セレクト信号やラッチクロックを出力する。

【0019】なお、減算器30は、バレルシフタ16に対して、バレルシフトすべきビット数すなわちシフト量を設定する。たとえば、第1信号が出力されたときにはシフト量として最初に残ビット数データが与えられ、ついで「有効ビット数ー残ビット数」すなわち減算結果の絶対値が与えられ、第2信号が出力されたときにはシフト量として残ビット数データが与えられ、第3信号が出力されたときにはシフト量として有効ビット数データが与えられる。

【0020】アドレスカウンタ34には、アドレスデコ 50 ダ36には、CPUアドレスバスとリード信号線とライ

8

ーダ36(図3)から与えられる初期アドレスライトクロックに応答して、メモリに記憶された可変長ビットデータの先頭アドレスデータがプリセットされる。アドレスカウンタ34にプリセットされたアドレスデータは、アービタ38から与えられるメモリデータライトクロックに応答してインクリメントされる。これにより、可変長ビットデータがメモリ内に複数ワードにわたって連続して記憶されている場合でも、アドレスカウンタ34に可変長ビットデータの先頭アドレスを1度プリセットするだけで、以後複数ワードにわたる可変長ビットデータを連続して読み出して第1レジスタ12にラッチすることができる。

【0021】アドレスセレクタ40は、CPUから与えられるCPUアドレスバスのアドレスデータまたはアドレスカウンタ34から与えられるアドレスデータのいずれか一方を切り換えてメモリに与える、この切り換えは、アービタ38からのセレクト信号に基づいて行われる。アービタ38は、可変長ビットデータ処理回路10の動作および可変長ビットデータ処理回路10とCPUとによるメモリアクセスのタイミングを制御するものである。

【0022】アービタ38には、図1に示すようにシス テムクロック,アドレスデコーダ36からのCPUメモ リリクエスト信号、およびタイミング発生器18からの セレクト信号およびイニシャルフラグとが与えられる。 アービタ38は、タイミング発生器18からのセレクト 信号が、第1レジスタ12にラッチされているデータを 第2レジスタ20に供給するようにセレクタ14を切り 換える信号であることを判断する。これに応答して、ア ービタ38は、アドレスカウンタ34をインクリメント させるカウント信号を発生し、これに続いてメモリから 与えられる可変長ビットデータを第1レジスタ12にラ ッチさせるメモリデータライトクロックを発生する。た だし、タイミング発生器18からのイニシャルフラグが イニシャル状態を示している場合は、カウント信号は発 生されない。また、アービタ38は、メモリデータライ トクロックを発生するのに先立って、アドレスセレクタ 40に対してアドレスカウンタ34からのアドレス信号 をメモリに供給するよう指示するセレクト信号を発生す 40 る。

【0023】一方、アービタ38は、アドレスデコーダ36(図3)からのCPUメモリリクエスト信号を監視することにより、CPUがメモリへのアクセスを要求しているか否かを判断する。そして、CPUがメモリへのアクセスを要求し、かつアドレスセレクタ40がアドレスカウンタ34からのアドレスデータをメモリに与えるよう切り換えられているときは、CPUに対してウェイト信号を与えて、CPUをウェイト状態にする。

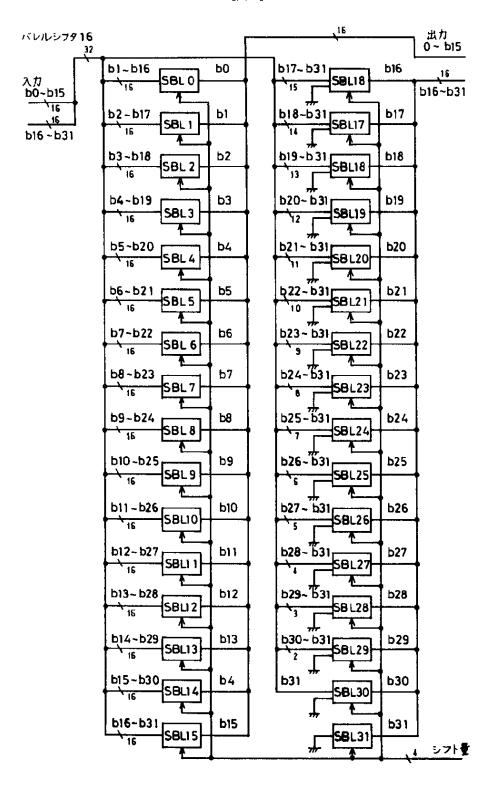

【0024】ここで、図3を参照して、アドレスデコーダ36には CPUアドレスバスとリード信号線とライ

ト信号線とが接続され、CPUからのアドレスデータと CPUからのリード信号とCPUからのライト信号とが 与えられる。CPUは、所定の大きさのメモリ空間を有 し、このメモリ空間内の所定のアドレスに上述のメモ リ、可変長ビットデータ処理スタート、第3レジスタ2 2および有効ビット数レジスタ28等が割り当てられて いる。アドレスデコーダ36は、常に、CPUからのア ドレスデータ、リード信号およびライト信号を監視し、 CPUがメモリの割り当てられているアドレスをアクセ スし、かつリード信号あるいはライト信号を出力してい 10 るときは、CPUメモリリクエスト信号を発生する。ま た、アドレスデコーダ36は、CPUが可変長ビットデ ータ処理をスタートさせるためのアドレスをアクセスし かつライト信号を出力しているときは、可変長ビットデ ータ処理回路 10 に可変長ビットデータ処理をスタート させるためのVBCスタート信号を発生する。また、ア ドレスデコーダ36は、CPUがアドレスカウンタの割 り当てられているアドレスをアクセスしかつライト信号 を出力しているときは、初期アドレスライトクロックを 発生する。さらに、アドレスデコーダ36は、CPUが 20 第3レジスタの割り当てられているアドレスをアクセス しかつリード信号を出力しているときは、CPUリード 信号を発生する。また、アドレスデコーダ36はCPU が有効ビット数レジスタ28の割り当てられているアド レスをアクセスしかつライト信号を出力しているとき

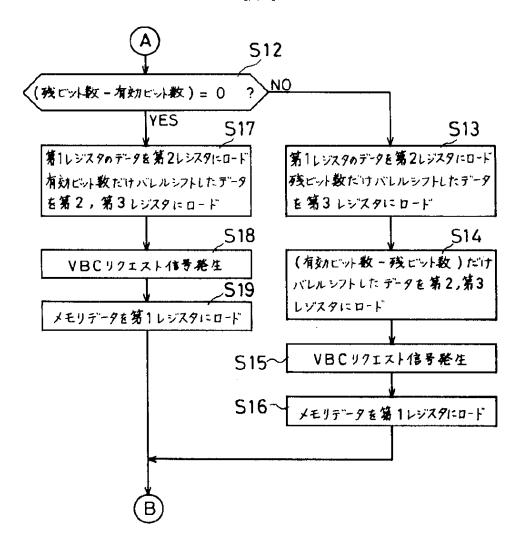

【0025】図4および図5を参照して、図1実施例の 動作を説明する。なお、図1実施例は、実際には、ハー ドウェアで構成されているが、図4および図5のフロー 図のように動作する。したがって、図4および図5フロ 30 一図に従って動作するマイクロコンピュータによって図 1回路が代替されてもよい。図4のステップS1からス テップS7までは、初期設定動作である。すなわち、C PUかつしたがってアドレスデコーダ36(図3)から のVBCスタート信号に応答してタイミング発生器18 がイネーブルされ、ステップS1において、タイミング 信号発生器18は、VBCリクエスト信号を出力する。 なお、アドレスデコーダ36は、上述のようにCPUか ら所定のアドレスデータが出力されたとき、VBCスタ モリアドレスカウンタ34(図1)に対してメモリリー ドアドレスをセットする。応じて、ステップS2におい て、メモリ(図示せず)からメモリデータが読み出さ れ、メモリデータライトクロックに応じてそのメモリデ ータが、第1レジスタ12にビット並列にロードされ る。そして、メモリデータライトクロックに応じて、ア ドレスカウンタ34がインクリメントされる。なお、メ モリ(図示せず)には、可変ビット長データ、すなわ ち、有効ビット数が変化するデータが効率よく(余白な しに) アドレス順次にストアされている。タイミング発 *50*

は、有効ビット数ライトクロック信号を発生する。

10

生器18は、このメモリデータライトクロックをカウン トして、次のステップS3において、再びVBCリクエ スト信号を発生する。したがって、次のステップS4に おいて、メモリ(図示せず)のインクリメントされたア ドレスからのメモリデータがビット並列に第1レジスタ 12にロードされるとともに、タイミング発生器18か らのセレクト信号が「1」であるため、第1レジスタ1 2のデータがセレクタ14を介して、ビット並列に第2 レジスタ20にロードされる。タイミング発生器18 は、メモリデータライトクロックをさらにカウントし て、次のステップS5において、再びVBCリクエスト 信号を発生する。したがって、次のステップS6におい て、メモリ(図示せず)からのメモリデータがビット並 列に第1レジスタ12にロードされるとともに、タイミ ング発生器18からのセレクト信号が「1」であるた め、第1レジスタ12のデータがセレクタ14を介し て、ビット並列に第2レジスタ20にロードされる。タ イミング発生器18からのイニシャルフラグが減算器3 0に与えられ、減算器30から「16」、すなわち「0 000」がバレルシフタ16に与えられる。第2レジス タ20のデータはバレルシフタ16を介して第3レジス タ22にロードされる。イニシャルカウンタ26は、こ こまでに3つのメモリデータライトクロックをカウント しているので、次のステップS7では、イニシャルエン ド信号を出力し、タイミング発生器18に与える。した がって、タイミング発生器18は、初期設定動作を終え

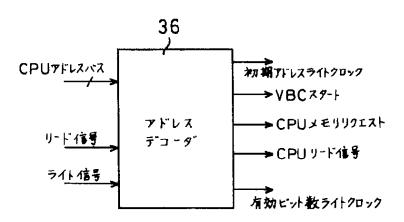

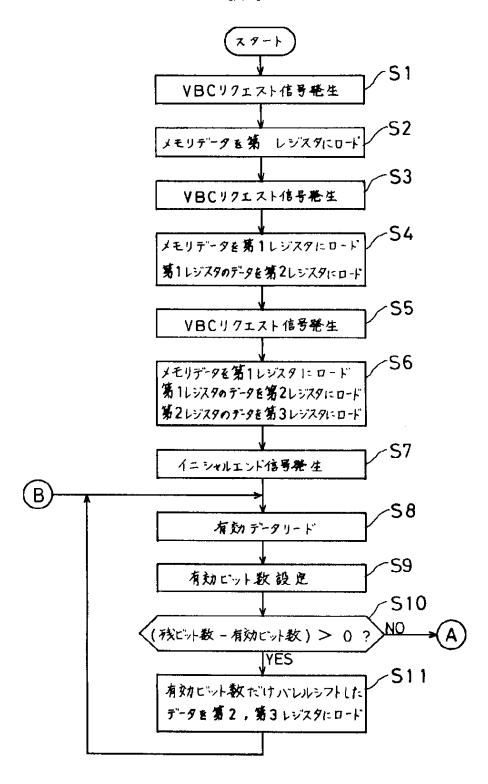

【0026】このようにして、図6に示すように、第1 レジスタ12、第2レジスタ20および第3レジスタ2 2に、それぞれ、データがロードされる。第3レジスタ 22には、最下位ビットから順に、16ビットのデータ  $a_0$ ,  $a_1$ ,  $a_2$ ,  $a_3$ ,  $a_4$ ,  $b_0$ ,  $b_1$ ,  $b_2$ ,  $b_3$ ,  $b_4$ ,  $b_5$ ,  $b_6$ ,  $c_0$ ,  $c_1$ ,  $c_2$ ,  $c_3$ ロードされ、第2レジスタ20には、最下位ビットから 順に、16ビットのデータ  $c_4$ ,  $c_5$ ,  $c_6$ ,  $c_7$ ,  $c_8$ ,  $c_9$ ,  $c_{10}$ ,  $c_{11}, c_{12}, c_{13}, d_0, d_1, d_2, d_3, d_4, d_5$ がロードされ、第1レ ジスタ12には、最下位ビットから順に、16ビットの データ $d_6$ ,  $e_0$ ,  $f_0$ ,  $f_1$ ,  $f_2$ ,  $f_3$ ,  $f_4$ ,  $f_5$ ,  $f_6$ ,  $f_7$ ,  $f_8$ ,  $f_9$ ,  $f_{10}$ ,  $g_0$ ,  $g_0$  $1, \mathbf{g}_2$  がロードされた状態を考える。アルファベット $\mathbf{a}_1$ b, c, …がそれぞれ異なるデータを示し、データ a の ート信号を出力する。このとき、CPUは、同時に、メ 40 有効ビット数は5ビット、データbの有効ビット数は7 ビット、データ c の有効ビット数は14ビット、データ dの有効ビット数は7ビット、データeの有効ビット数 は1ビット、データfの有効ビット数は11ビット、そ してデータgの有効ビット数は未定である。

> 【0027】次のステップS8において、CPU(図示 せず) は第3レジスタ22から有効データにa<sub>0</sub>-a<sub>4</sub> をリ ードする。ステップS9で、CPUライトデータとし て、データaの有効ビット数である「5」がCPUから 出力される。応じて、アドレスデコーダ36(図3)か ら有効ビット数ライトクロックが出力されるので、有効

ビット数レジスタ28に、「5」のデータが書き込まれ る。

【0028】次のステップS10において、減算器30 が「残ビット数-有効ビット数」の演算を実行する。こ こで、残ビット数とは、第2レジスタ20に保持されて いるデータのうち、バレルシフトの結果生じた「0」以 外のデータ、たとえば、図6におけるc4-c13およびd0-d 6 の16ビットのデータあるいは図7におけるc9-c13お よびdo-doの11ビットのデータを意味する。図6の例 では、第2レジスタ20の残ビット数は「16」である ため、ステップS10の減算結果は「16-5=11」 で正となり、ステップS10では「YES」と判断され る。減算器30からは、このとき、バレルシフタ16に おけるシフト量として有効ビット数である「5」をバレ ルシフタ16に指示する。したがって、次のステップS 11において、有効ビット数「5」だけバレルシフトし たデータを第2レジスタ20および第3レジスタ22に ロードする。その結果が、図7に示される。図7では、 第1レジスタ12のデータはそのまま変化せず、第3レ ジスタ22に保持されていた5ビットのデータaが第3 レジスタ22から押し出される。したがって、第3レジ スタ22には、16ビットのデータ  $b_0, b_1, b_2, b_3, b_4,$  $b_5, b_6, c_0, c_1, c_2, c_3, c_4, c_5, c_6, c_7, c_8$ が保持される。な お、減算器30からのボロー信号もゼロ信号もともに 「0」であるので、タイミング発生器18からは「0」 のセレクト信号が出力される。応じて、セレクタ14は バレルシフタ16からのデータを選択する。したがっ T、第2レジスタ20には11ビットのデータ $c_9$ ,  $c_{10}$ , c11, C12, C13, d0, d1, d2, d3, d4, d5 と5 ビットの「0」が保 持される。「0」は、バレルシフタ16によって第2レ *30* ジスタ20のデータを5ビットバレルシフトした結果、 第2レジスタ20に書き込まれる。

【0029】図7の状態において、第3レジスタ22の データbの有効ビット数は「7」であり、第2レジスタ 20の残ビット数は「11」である。したがって、ここ で再び、ステップS8からステップS11が繰り返し実 行される。その結果、図8に示すように、第3レジスタ 22からは7ビットのデータbが排出され、データbは CPUリードデータとして取り込まれる。そして、第3 レジスタ22には、16ビットのデータ $c_0$ ,  $c_1$ ,  $c_2$ ,  $c_3$ ,  $c_4$ ,  $c_5$ ,  $c_6$ ,  $c_7$ ,  $c_8$ ,  $c_9$ ,  $c_{10}$ ,  $c_{11}$ ,  $c_{12}$ ,  $c_{13}$ ,  $d_0$ ,  $d_1$  が保持さ れ、第2レジスタ20には、4ビットのデータ $d_2, d_3$ , d₄,d₅ と12ビットの「0」が保持される。先に5ビッ トの「0」があり、かつ新たに7ビットのバレルシフト が行われるのであるから、この段階で第2レジスタ20 の「0」は12ビットになる。

【0030】図8の状態において、第3レジスタ22の データ c の有効ビット数は「14」であり、第2レジス タ20の残ビット数は「4」である。したがって、減算 器30の減算の結果は「4-14=-10」となり、ボ 50 長ビットデータ列をメモリ内にアドレス順にストアして

12

ロー信号が出力され、ステップS10では「NO」と判 断される。そのため、プロセスは図5のステップS12 に進み、このステップS12において、「残ビット数-有効ビット数」の減算結果が「0」であるかどうかを判 断する。上述の例では、減算結果は「-10」であるた め、このステップS12では「NO」と判断され、した がって、プロセスはステップS13に進む。

【0031】ボロー信号に応じて、タイミング発生器1 8は「0」のセレクト信号を出力する。また、減算器3 0からは、減算結果が負になったので、シフト量とし て、残ビット数である「4」をバレルシフタ16に与え る。したがって、ステップS13では、図9に示すよう に、まず、第2レジスタ20および第3レジスタ22の データを4ビットバレルシフトし、それを第2レジスタ 20および第3レジスタ22にロードする。このとき、 バレルシフタ16の下位16ビットのデータは、 $c_4$ ,  $c_5$ ,  $c_6, c_7, c_8, c_9, c_{10}, c_{11}, c_{12}, c_{13}, d_0, d_1, d_2, d_3, d_4, d_5$   $\succeq$ り、上位16ビットは全て「0」になる。ここで、次に タイミング発生器18からの「1」のセレクト信号に応 20 答して、セレクタ14が第1レジスタ12のデータを選 択しているため、第2レジスタ20には第1レジスタ1 2のデータがビット並列でロードされ、第2レジスタ2 0は16ビットのデータ $d_6$ ,  $e_0$ ,  $f_0$ ,  $f_1$ ,  $f_2$ ,  $f_3$ ,  $f_4$ ,  $f_5$ ,  $f_6$ , f $7, f_8, f_9, f_{10}, g_0, g_1, g_2$ が保持される。

【0032】次のステップS14では、減算器30から 「有効ビット数-残ビット数」のシフト量がバレルシフ タ16に指示される。図8の状態では、第3レジスタ2 2の有効ビット数は「14」であり、第2レジスタ20 の残ビット数は「4」である。したがって、このときの シフト量は「10」である。したがって、ステップS1 4において、第2レジスタ20および第3レジスタ22 のデータをバレルシフタ16によって10ビットバレル シフトしたデータを第2レジスタ20および第3レジス タ22にセレクタ14を通してロードする。その結果、 第3レジスタ22には、16ビットのデータ $d_0$ ,  $d_1$ ,  $d_2$ ,  $d_3$  $3, d_4, d_5, d_6, e_0, f_0, f_1, f_2, f_3, f_4, f_5, f_6, f_7$  が保持され、 第2レジスタ20には6ビットのデータ $f_8, f_9, f_{10}, g_0, g$  $_{1},\mathbf{g}_{2}$ と10ビットの「0」とが保持される。

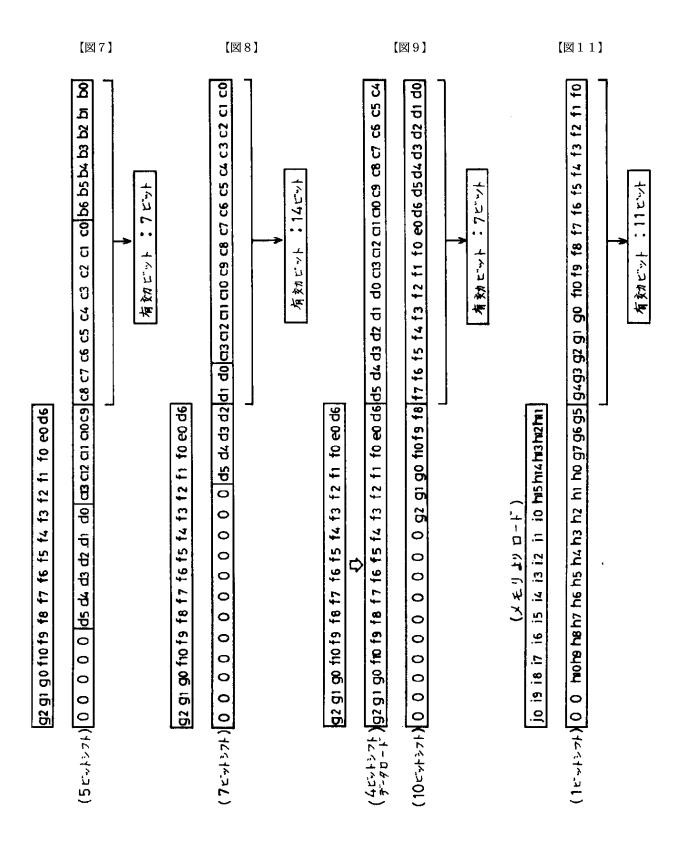

【0033】次のステップS15においてタイミング発 生器18からVBCリクエスト信号が出力され、応じ て、メモリ(図示せず)から次のメモリデータが読み出 される。したがって、ステップS16では、図10に示 すように、メモリデータが第1レジスタ12にビット並 列にロードされ、第1レジスタ12には16ビットのデ 一夕  $g_3$ ,  $g_4$ ,  $g_5$ ,  $g_6$ ,  $g_7$ ,  $h_0$ ,  $h_1$ ,  $h_2$ ,  $h_3$ ,  $h_4$ ,  $h_5$ ,  $h_6$ ,  $h_7$ ,  $h_8$ ,  $h_9$ , h10 が保持される。

【0034】なお、タイミング発生器18は、メモリか ら第1レジスタ12にデータをロードする毎に、メモリ アドレスカウンタ34をインクリメントするため、可変

おくだけで、それぞれの可変長ビットデータは自動的に 順次メモリから第1レジスタ12ヘロードされる。再び ステップS12が実行されると、図9の状態では、第3 レジスタ22のデータdの有効ビット数は「7」で残ビ ット数は「4」であり、その結果、ステップS13から ステップS16が実行される。すなわち、ステップS1 3を経て、図10に示すように、第3レジスタ22には 16ビットのデータ $d_6$ ,  $e_0$ ,  $f_0$ ,  $f_1$ ,  $f_2$ ,  $f_3$ ,  $f_4$ ,  $f_5$ ,  $f_6$ ,  $f_7$ ,  $f_8$ ,  $f_9$ ,  $f_{10}$ ,  $g_0$ ,  $g_1$ ,  $g_2$ ,  $g_3$  が保持され、第2レジスタ20 には16ビットのデータ $g_3$ ,  $g_4$ ,  $g_5$ ,  $g_6$ ,  $g_7$ ,  $h_0$ ,  $h_1$ ,  $h_2$ ,  $h_3$ ,  $h_4$ ,  $h_5$ ,  $h_6$ ,  $h_7$ ,  $h_8$ ,  $h_9$ ,  $h_{10}$  が保持される。同時に、7ビッ トのデータdがCPUリードデータとして取り込まれ る。その後のステップS15およびステップS16を経 て、図10に示すように、第3レジスタ22には16ビ ットのデータ  $e_0$ ,  $f_0$ ,  $f_1$ ,  $f_2$ ,  $f_3$ ,  $f_4$ ,  $f_5$ ,  $f_6$ ,  $f_7$ ,  $g_0$ ,  $g_1$ ,  $g_2$  が 保持され、第2レジスタ20には、15ビットのデータ  $g_4$ ,  $g_5$ ,  $g_6$ ,  $g_7$ ,  $h_0$ ,  $h_1$ , 前 $h_2$ ,  $h_3$ ,  $h_4$ ,  $h_5$ ,  $h_6$ ,  $h_7$ ,  $h_8$ ,  $h_9$ ,  $h_{10}$  と 1ビットの「0」が保持され、第1レジスタ12にはメ モリ (図示せず) からメモリデータh11,h12,h13,h14,h 15,  $i_0$ ,  $i_1$ ,  $i_2$ ,  $i_3$ ,  $i_4$ ,  $i_5$ ,  $i_6$ ,  $i_7$ ,  $i_8$ ,  $i_9$ ,  $j_0$  がロードされ 20 る。

【0035】図10の状態では、第3レジスタ22のデ ータeの有効ビット数は「1」であり、残ビット数は 「15」であるので、次に実行されるステップS10で 「YES」と判断され、再び、ステップS11が実行さ れる。その結果、図11に示すように、第3レジスタ2 2には16ビットのデータ $f_0$ ,  $f_1$ ,  $f_2$ ,  $f_3$ ,  $f_4$ ,  $f_5$ ,  $f_6$ ,  $f_7$ ,  $g_0, g_1, g_2, g_3, g_4$ が保持され、第2レジスタ20には、1 4 ビットのデータ  $g_5, g_6, g_7, h_0, h_1, h_2, h_3, h_4, h_5, h_6, h_7,$  $h_8, h_9, h_{10}$  と 2 ビットの「0」が保持される。

【0036】図11の状態では、第3レジスタ22のデ ータ f の有効ビット数は「11」であり、残ビット数は 「14」であるので、次に実行されるステップS10で 「YES」と判断され、再び、ステップS11が実行さ れる。その結果、図12に示すように、第3レジスタ2 2には16ビットのデータ $g_0, g_1, g_2, g_3, g_4, g_5, g_6, g$  $7, h_0, h_1, h_2, h_3, h_4, h_5, h_6, h_7$  が保持され、第2レジスタ 20には、3ビットのデータ $h_8$ ,  $h_9$ ,  $h_{10}$  と13ビットの 「0」が保持される。このとき、第1レジスタ12のデ 一夕は $h_{11}$ ,  $h_{12}$ ,  $h_{13}$ ,  $h_{14}$ ,  $h_{15}$ ,  $i_0$ ,  $i_1$ ,  $i_2$ ,  $i_3$ ,  $i_4$ ,  $i_5$ ,  $i_6$ ,  $i_7$ , i<sub>8</sub>, i<sub>9</sub>, j<sub>0</sub>で不変である。

【0037】図12の状態では、第3レジスタ22のデ ータgの有効ビット数は「8」であり、残ビット数は 「3」であるため、次に実行されるステップS10およ びステップS12でともに、「NO」と判断される。そ のため、ステップS13からステップS16までが再び 実行される。その結果が図13に示される。図13の状 態において、第3レジスタ22のデータhの有効ビット 数は「16」であり、第2レジスタ20の残ビット数は 「11」である。したがって、減算器30の減算の結果 50 は「11-16=-5」となり、ボロー信号が出力さ れ、ステップS10では「NO」と判断される。そのた め、ステップS12において、「残ビット数-有効ビッ ト数」の減算結果が「0」であるかどうかを判断する。 上述の例では、減算結果は「-5」であるため、このス テップS12では「NO」と判断され、したがって、プ ロセスはステップS13に進む。

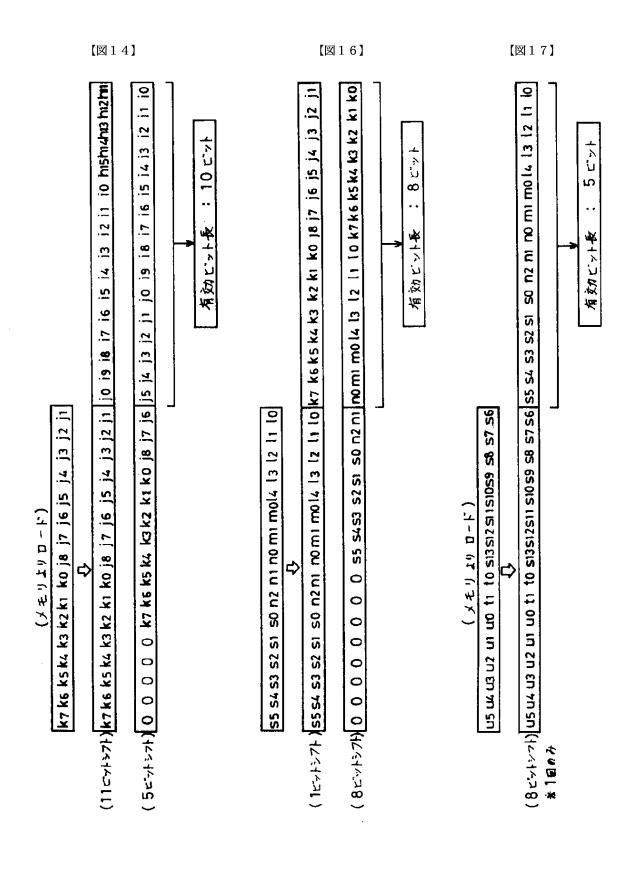

【0038】ボロー信号に応じて、タイミング発生器1 8は「0」のセレクト信号を出力する。また、減算器3 0からは、減算結果が負になったので、シフト量とし て、残ビット数である「11」をバレルシフタ16に与 える。したがって、ステップS13では、図14に示す ように、まず、第2レジスタ20および第3レジスタ2 2のデータを11ビットバレルシフトし、それを第2レ ジスタ20および第3レジスタ22にロードする。この とき、バレルシフタ16の下位16ビットのデータは、  $h_{11}$ ,  $h_{12}$ ,  $h_{13}$ ,  $h_{14}$ ,  $h_{15}$ ,  $i_0$ ,  $i_1$ ,  $i_2$ ,  $i_3$ ,  $i_4$ ,  $i_5$ ,  $i_6$ ,  $i_7$ ,  $i_8$ ,  $i_9$ , j<sub>0</sub>となり、上位16ビットのデータは全て「0」とな る。ここで、次にタイミング発生器18からの「1」の セレクト信号に応答して、セレクタ14が第1レジスタ 12のデータを選択するため、第2レジスタ20には第 1レジスタ12のデータがビット並列でロードされ、第 2 レジスタ 2 0 には 1 6 ビットのデータ $j_1, j_2, j_3, j_4,$ j5,j6,j7,j8,k0,k1,k2,k3,k4,k5,k6,k7 が保持される。 【0039】次のステップS14では、減算器30から 「有効ビット数-残ビット数」のシフト量がバレルシフ タ16に指示される。図14の状態では、第3レジスタ 22の有効ビット数は「16」であり、第2レジスタ2 0の残ビット数は「11」である。したがって、このと きのシフト量は「5」である。したがって、ステップS 14において、第2レジスタ20および第3レジスタ2 2のデータをバレルシフタ16によって5ビットバレル シフトしたデータを第2レジスタ20および第3レジス タ22にセレクタ14を通してロードする。その結果、 第3レジスタ22には、16ビットのデータ $i_0$ ,  $i_1$ ,  $i_2$ , i $3, i_4, i_5, i_6, i_7, i_8, i_9, j_0, j_1, j_2, j_3, j_4, j_5$  が保持され、 第2レジスタ20には11ビットのデータ $j_6, j_7, j_8, k_0$  $\mathbf{k}_1$ ,  $\mathbf{k}_2$ ,  $\mathbf{k}_3$ ,  $\mathbf{k}_4$ ,  $\mathbf{k}_5$ ,  $\mathbf{k}_6$ ,  $\mathbf{k}_7$  と  $\mathbf{5}$  ビットの「 $\mathbf{0}$ 」とが保持され

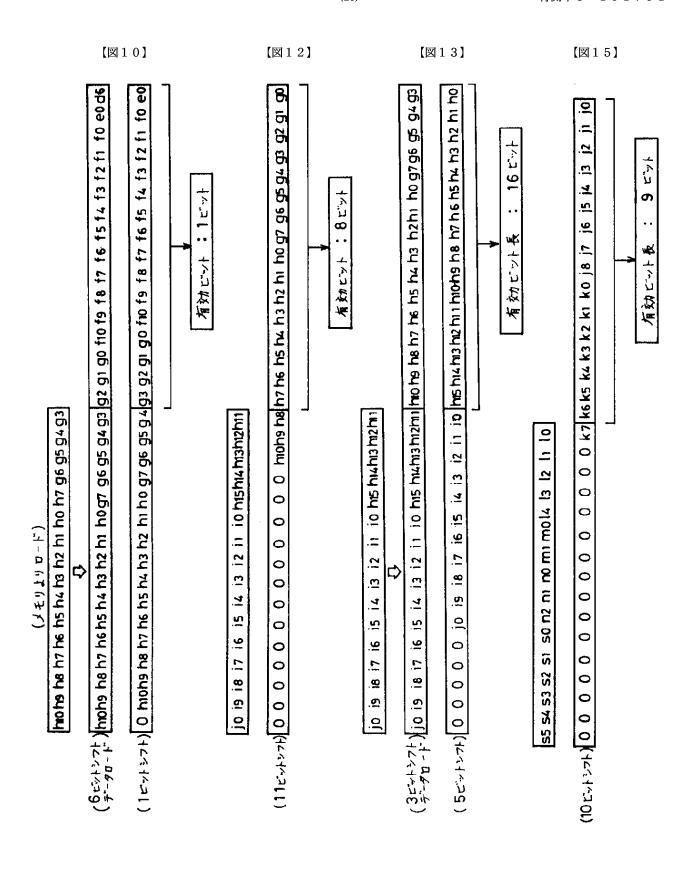

【0040】次のステップS15においてタイミング発 生器18からVBCリクエスト信号が出力され、応じ て、メモリ (図示せず) から次のメモリデータが読み出 される。したがって、ステップS16では、図15に示 すように、メモリデータが第1レジスタ12にビット並 列にロードされ、第1レジスタ12には16ビットのデ  $-9l_0, l_1, l_2, l_3, l_4, m_0, m_1, n_0, n_1, n_2, s_0, s_1, s_2, s_3, s_4, s_6$ 5 が保持される。

【0041】図14の状態において、第3レジスタ22 のデータiの有効ビット数は「10」であり、第2レジ スタ20の残ビット数は「11」である。したがって、

16 タ16に指示される。図15の状態では、第3レジスタ 22の有効ビット数は「9」であり、第2レジスタ20 の残ビット数は「1」である。したがって、このときの シフト量は「8」である。したがって、ステップS14 において、第2レジスタ20および第3レジスタ22の データをバレルシフタ16によって8ビットバレルシフ トしたデータを第2レジスタ20および第3レジスタ2 2にセレクタ14を通してロードする。その結果、第3 レジスタ22に保持されていた9ビットのデータjが第 3レジスタ22から押し出される。そして、図16に示 すように、第3レジスタ22には、16ビットのデータ  $k_0$ ,  $k_1$ ,  $k_2$ ,  $k_3$ ,  $k_4$ ,  $k_5$ ,  $k_6$ ,  $k_7$ ,  $l_0$ ,  $l_1$ ,  $l_2$ ,  $l_3$ ,  $l_4$ ,  $m_0$ ,  $m_1$ ,  $n_0$ 保持され、第2レジスタ20には8ビットのデータn1,n  $2, S_0, S_1, S_2, S_3, S_4, S_5$  と8ビットの「0」とが保持され る。

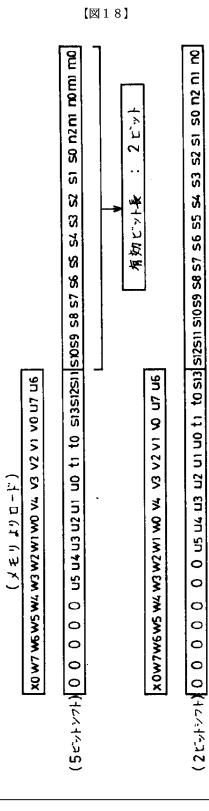

【0045】次のステップS15においてタイミング発生器18からVBCリクエスト信号が出力され、応じて、メモリ(図示せず)から次のメモリデータが読み出される。したがって、ステップS16では、図17に示すように、メモリデータが第1レジスタ12にビット並列にロードされ、第1レジスタ12は16ビットのデータ $\mathbf{s}_6$ ,  $\mathbf{s}_7$ ,  $\mathbf{s}_8$ ,  $\mathbf{s}_9$ ,  $\mathbf{s}_{10}$ ,  $\mathbf{s}_{11}$ ,  $\mathbf{s}_{12}$ ,  $\mathbf{s}_{13}$ ,  $\mathbf{t}_0$ ,  $\mathbf{t}_1$ ,  $\mathbf{u}_0$ ,  $\mathbf{u}_1$ ,  $\mathbf{u}_2$ ,  $\mathbf{u}_3$ ,  $\mathbf{u}_4$ ,  $\mathbf{u}_5$  が保持される。

【0046】再びステップS12が実行されると、図1 6の状態では、第3レジスタ22のデータkの有効ビッ ト数は「8」で残ビット数は「8」であり、その結果、 図5のステップS17からステップS19が実行され る。まず、ステップS17において、タイミング発生器 18からの「1」のセレクト信号に応答して、セレクタ 14が第1レジスタ12のデータを選択しているため、 第2レジスタ20には第1レジスタ12のデータがビッ ト並列でロードされ、第2レジスタ20には16ビット のデータ $s_6$ ,  $s_7$ ,  $s_8$ ,  $s_9$ ,  $s_{10}$ ,  $s_{11}$ ,  $s_{12}$ ,  $s_{13}$ ,  $t_0$ ,  $t_1$ ,  $u_0$ ,  $u_1$ , u2, u3, u4, u5 が保持される。それとともに、減算器30 から有効ビット数に相当するシフト量がバレルシフタ1 6に指示される。図16の状態では、第3レジスタ22 の有効ビット数は「8」である。したがって、このとき のシフト量は「8」である。したがって、ステップS1 7において、第2レジスタ20および第3レジスタ22 40 のデータをバレルシフタ16によって8ビットバレルシ フトしたデータを第2レジスタ20および第3レジスタ 22にセレクタ14を通してロードする。その結果、第 3レジスタ22に保持されていた8ビットのデータkが 第3レジスタ22から押し出される。そして、図17に 示すように、第3レジスタ22には、16ビットのデー 夕 $l_0$ ,  $l_1$ ,  $l_2$ ,  $l_3$ ,  $l_4$ ,  $m_0$ ,  $m_1$ ,  $n_0$ ,  $n_1$ ,  $n_2$ ,  $s_0$ ,  $s_1$ ,  $s_2$ ,  $s_3$ ,  $s_4$ ,  $s_5$ が保持され、第2レジスタ20には16ビットのデータ S6, S7, S8, S9, S10, S11, S12, S13, t0, t1, U0, U1, U2, U3, U4, U 5 が保持される。

∅ 【0047】次のステップS18においてタイミング発

減算器30の減算の結果は「11-10=1」となり、 ステップS10では「YES」と判断される。減算器3 0からは、このとき、バレルシフタ16におけるシフト 量として有効ビット数である「10」をバレルシフタ1 6に指示する。したがって、次のステップS11におい て、有効ビット数「10」だけバレルシフトしたデータ を第2レジスタ20および第3レジスタ22にロードす る。その結果が、図15に示される。図15では、第1 レジスタ12のデータはそのまま変化せず、第3レジス タ22に保持されていた10ビットのデータiが第3レ ジスタ22から押し出される。したがって、第3レジス 922には、16ビットのデータ $j_0$ ,  $j_1$ ,  $j_2$ ,  $j_3$ ,  $j_4$ ,  $j_5$ ,  $j_6, j_7, j_8, k_0, k_1, k_2, k_3, k_4, k_5, k_6$ が保持される。なお、 減算器30からのボロー信号もゼロ信号もともに「0」 であるので、タイミング発生器18からは「0」のセレ クト信号が出力される。応じて、セレクタ14はバレル シフタ16からのデータを選択する。したがって、第2 レジスタ20には1ビットのデータk7と15ビットの 「0」が保持される。「0」は、バレルシフタ16によ って第2レジスタ20のデータを10ビットバレルシフ トした結果、第2レジスタ20に書き込まれる。

【0042】図15の状態において、第3レジスタ22のデータ」の有効ビット数は「9」であり、第2レジスタ20の残ビット数は「1」である。したがって、減算器30の減算の結果は「1-9=-8」となり、ボロー信号が出力され、ステップS10では「NO」と判断される。そのため、ステップS12において、「残ビット数-有効ビット数」の減算結果が「0」であるかどうかを判断する。上述の例では、減算結果は「-8」であるため、このステップS12では「NO」と判断され、し 30たがって、プロセスはステップS13に進む。

【0043】ボロー信号に応じて、タイミング発生器1 8は「0」のセレクト信号を出力する。また、減算器3 0からは、減算結果が負になったので、シフト量とし て、残ビット数である「1」をバレルシフタ16に与え る。したがって、ステップS13では、図16に示すよ うに、まず、第2レジスタ20および第3レジスタ22 のデータを1ビットバレルシフトし、それを第2レジス タ20および第3レジスタ22にロードする。このと き、バレルシフタ16の下位16ビットのデータは、  $j_1, j_2, j_3, j_4, j_5, j_6, j_7, j_8, k_0, k_1, k_2, k_3, k_4, k_5, k_6, k_7 \succeq$ なり、上位16ビットは全て「0」になる。ここで、次 にタイミング発生器18からの「1」のセレクト信号に 応答して、セレクタ14が第1レジスタ12のデータを 選択するため、第2レジスタ20には第1レジスタ12 のデータがビット並列でロードされ、第2レジスタ20 は16ビットのデータ  $l_0$ ,  $l_1$ ,  $l_2$ ,  $l_3$ ,  $l_4$ ,  $m_0$ ,  $m_1$ ,  $n_0$ ,  $n_1$ , n<sub>2</sub>, s<sub>0</sub>, s<sub>1</sub>, s<sub>2</sub>, s<sub>3</sub>, s<sub>4</sub>, s<sub>5</sub> が保持される。

【0044】次のステップS14では、減算器30から 「有効ビット数-残ビット数」のシフト量がバレルシフ *50*

生器18からVBCリクエスト信号が出力され、応じ て、メモリ(図示せず)から次のメモリデータが読み出 される。したがって、ステップS19では、図18に示 すように、メモリデータが第1レジスタ12にビット並 列にロードされ、第1レジスタ12には16ビットのデ 一夕 $u_6$ ,  $u_7$ ,  $v_0$ ,  $v_1$ ,  $v_2$ ,  $v_3$ ,  $v_4$ ,  $w_0$ ,  $w_1$ ,  $w_2$ ,  $w_3$ ,  $w_4$ ,  $w_5$ ,  $w_6$ ,  $w_7$ , x。が保持される。

【0048】図17の状態において、第3レジスタ22 のデータ1の有効ビット数は「5」であり、第2レジス 夕20の残ビット数は「16」である。したがって、減 *10* スタ22から有効データが取り出される。 算器30の減算の結果は「16-5=11」となり、ス テップS10では「YES」と判断される。減算器30 からは、このとき、バレルシフタ16におけるシフト量 として有効ビット数である「5」をバレルシフタ16に 指示する。したがって、次のステップS11において、 有効ビット数「5」だけバレルシフトしたデータを第2 レジスタ20および第3レジスタ22にロードする。そ の結果が、図18の上部で示される。この状態では、第 1レジスタ12のデータはそのまま変化せず、第3レジ スタ22に保持されていた5ビットのデータ1が第3レ 20 す図解図である。 ジスタ22から押し出される。したがって、第3レジス 922には、16ビットのデータ $\mathbf{m}_0$ ,  $\mathbf{m}_1$ ,  $\mathbf{n}_0$ ,  $\mathbf{n}_1$ ,  $\mathbf{n}_2$ ,  $\mathbf{s}_0$ , s1, s2, s3, s4, s5, s6, s7, s8, s9, s10 が保持される。な お、減算器30からのボロー信号もゼロ信号もともに 「0」であるので、タイミング発生器18からは「0」 のセレクト信号が出力される。応じて、セレクタ14は バレルシフタ16からのデータを選択する。したがっ T、第2レジスタ20には11ビットのデータ $s_{11}, s_{12}$ ,  $s_{13}, t_{0}, t_{1}, u_{0}, u_{1}, u_{2}, u_{3}, u_{4}, u_{5}$  と5ビットの「0」が保 持される。「0」は、バレルシフタ16によって第2レ 30 示す図解図である。 ジスタ20のデータを10ビットバレルシフトした結 果、第2レジスタ20に書き込まれる。

【0049】図18の上部の状態において、第3レジス タ22のデータmの有効ビット数は「2」であり、第2 レジスタ20の残ビット数は「11」である。したがっ て、減算器30の減算の結果は「11-2=9」とな り、ステップS10では「YES」と判断される。減算 器30からは、このとき、バレルシフタ16におけるシ フト量として有効ビット数である「2」をバレルシフタ 16に指示する。したがって、次のステップS11にお 40 示す図解図である。 いて、有効ビット数「2」だけバレルシフトしたデータ を第2レジスタ20および第3レジスタ22にロードす る。その結果が、図18の下部に示される。図18の下 部では、第1レジスタ12のデータはそのまま変化せ ず、第3レジスタ22に保持されていた2ビットのデー 夕mが第3レジスタ22から押し出される。したがっ T、第3レジスタ22には、16ビットのデータ $n_0$ ,  $n_1$ ,  $n_2$ ,  $s_0$ ,  $s_1$ ,  $s_2$ ,  $s_3$ ,  $s_4$ ,  $s_5$ ,  $s_6$ ,  $s_7$ ,  $s_8$ ,  $s_9$ ,  $s_{10}$ ,  $s_{11}$ ,  $s_{12}$ 保持される。なお、減算器30からのボロー信号もゼロ 信号もともに「0」であるので、タイミング発生器18 50

18

からは「0」のセレクト信号が出力される。応じて、セ レクタ14はバレルシフタ16からのデータを選択す る。したがって、第2レジスタ20には9ビットのデー  $9s_{13}, t_0, t_1, u_0, u_1, u_2, u_3, u_4, u_5$  と7ビットの「0」が 保持される。「0」は、バレルシフタ16によって第2 レジスタ20のデータを10ビットバレルシフトした結 果、第2レジスタ20に書き込まれる。

【0050】このようにして、上述の実施例によれば、 最大2回のバレルシフト動作を実行するだけで第3レジ

### 【図面の簡単な説明】

【図1】この発明の一実施例を示すブロック図である。

【図2】図1実施例のバレルシフタを詳細に示すブロッ ク図である。

【図3】図1実施例のアドレスデコーダを示すブロック 図である。

【図4】図1実施例の動作を示すフロー図である。

【図5】図1実施例の動作を示すフロー図である。

【図6】図1実施例の動作を示す各レジスタの状態を示

【図7】図1実施例の動作を示す各レジスタの状態を示 す図解図である。

【図8】図1実施例の動作を示す各レジスタの状態を示 す図解図である。

【図9】図1実施例の動作を示す各レジスタの状態を示 す図解図である。

【図10】図1実施例の動作を示す各レジスタの状態を 示す図解図である。

【図11】図1実施例の動作を示す各レジスタの状態を

【図12】図1実施例の動作を示す各レジスタの状態を 示す図解図である。

【図13】図1実施例の動作を示す各レジスタの状態を 示す図解図である。

【図14】図1実施例の動作を示す各レジスタの状態を 示す図解図である。

【図15】図1実施例の動作を示す各レジスタの状態を 示す図解図である。

【図16】図1実施例の動作を示す各レジスタの状態を

【図17】図1実施例の動作を示す各レジスタの状態を 示す図解図である。

【図18】図1実施例の動作を示す各レジスタの状態を 示す図解図である。

## 【符号の説明】

10 …可変長ビットデータ処理回路

12 …第1レジスタ

14 …セレクタ

16 …バレルシフタ

20 …第2レジスタ

22 …第3レジスタ

【図2】

【図3】

【図5】

【図4】

フロントページの続き

(72)発明者 寺川 英明 兵庫県川西市中央町3番6号 株式会社ク リエイティブ・デザイン内