# MOS Integrated Circuit $\mu PD70732$

# V810<sup>™</sup> 32-BIT MICROPROCESSOR

The µPD70732 (a.k.a. V810) microprocessor is NEC's first microprocessor of the V810 family<sup>™</sup> for embedded control applications.

The V810 employs a RISC architecture for embedded control applications. This product has high-speed real time response, high-speed integer operation instruction, bit string instruction, floating-point operation instruction, and significantly high cost performance is realized for applications such as facsimile, digital PPC, word processor, image processor, real time control device, etc.

The functions are described in detail in the following User's Manuals, which should be read before starting design work.

- V805™, V810 User's Manual Hardware : U10661E

- V810 Family User's Manual Architecture : U10082E

#### Features

JEC

$\bigcirc$  High-performance 32-bit architecture for embedded control application

- 32-bit separate address/data bus

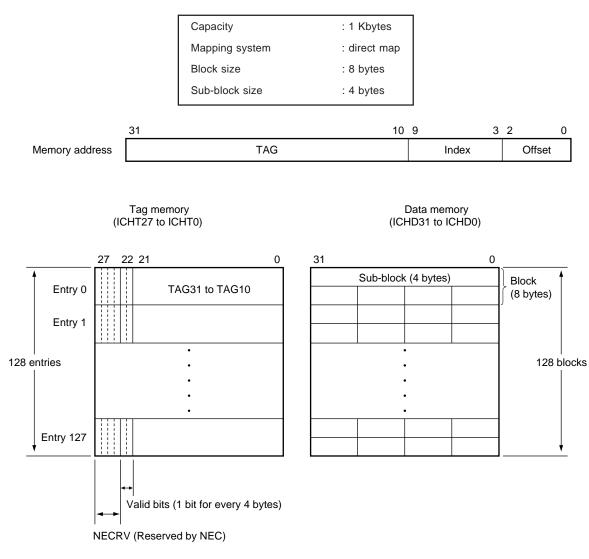

- 1-Kbyte cache memory

- Pipeline structure of 1 clock pitch

- 16-bit fixed instructions (with some exceptions)

- 32-bit general-purpose registers: 32

- 4-Gbyte linear address space

- · Register/flag hazard interlocked by hardware

- Dynamic bus sizing function (16 bits)

- $\bigcirc$  16-bit bus fixing function

- 16-bit bus system can be configured.

- $\bigcirc$  Instructions ideal for various application fields

- Floating-point operation instructions (based upon IEEE754 data format)

- Bit string instructions

- 16 levels of high-speed interrupt responses

- Clock can be stopped by internal static operation

- Maximum operating frequency: 16/20/25 MHz

- $\bigcirc$  Low voltage: V\_DD = 2.7 to 3.6 V (Max. 16 MHz)

- $V_{DD} = 2.2$  to 3.6 V (Max. 10 MHz)

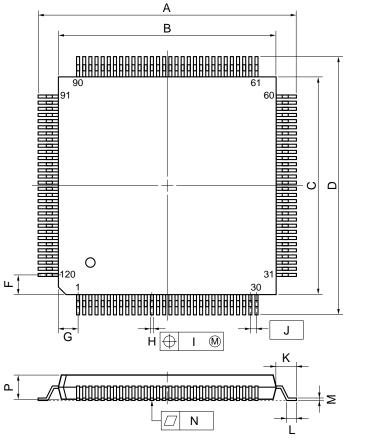

- $\bigcirc$  Small package versions available (14 x 14 mm fine-pitch TQFP)

The information in this document is subject to change without notice.

#### **Ordering Information**

| Part Number       | Package                                        | Max. operating freq. (MHz) |

|-------------------|------------------------------------------------|----------------------------|

| µPD70732GD-16-LBB | 120-pin plastic QFP (28 x 28 mm)               | 16                         |

| µPD70732GD-20-LBB | 120-pin plastic QFP (28 x 28 mm)               | 20                         |

| µPD70732GD-25-LBB | 120-pin plastic QFP (28 x 28 mm)               | 25                         |

| µPD70732GC-25-9EV | 120-pin plastic TQFP (Fine pitch) (14 x 14 mm) | 25                         |

| μPD70732R-25      | 176-pin ceramic PGA (Seam weld)                | 25                         |

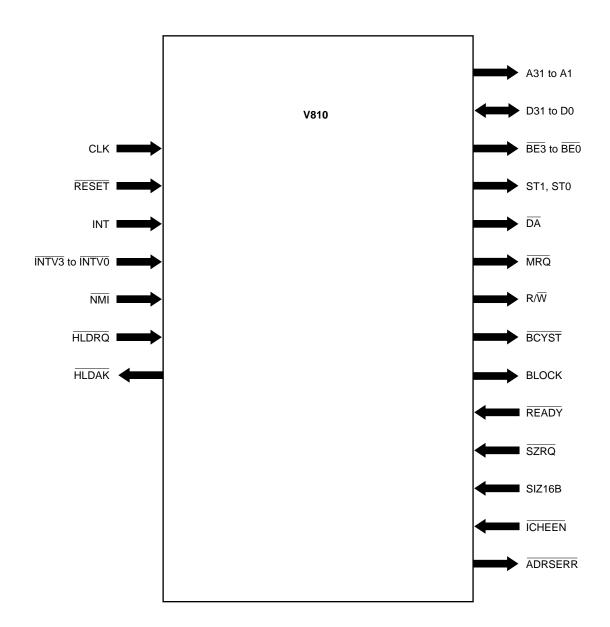

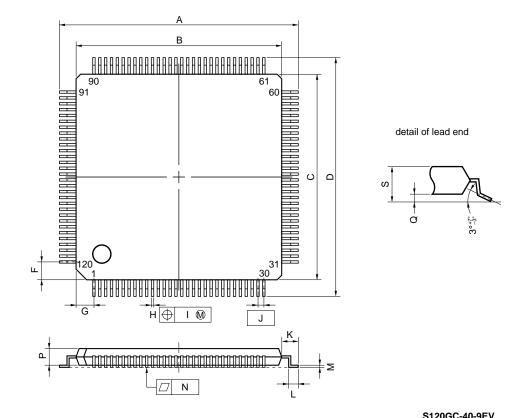

#### **Pin Outline**

$\star$

2

#### **Pin Configuration**

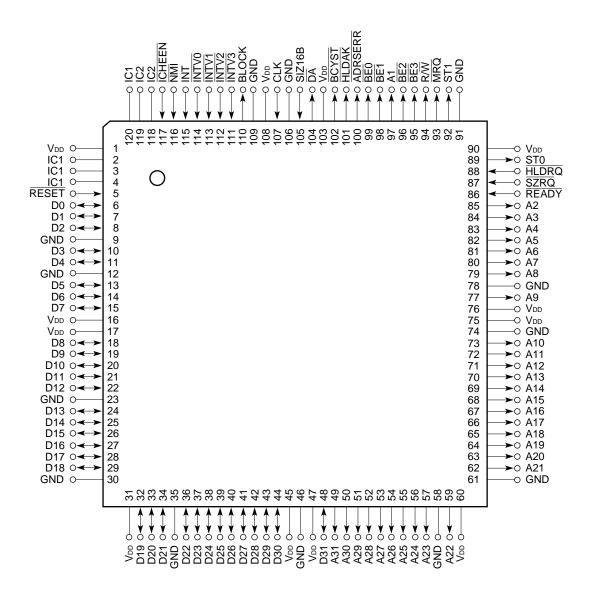

• 120-pin plastic QFP (28 x 28 mm) (Top View) µPD70732GD-xx-LBB

Cautions 1. Leave the IC1 pin open.

2. Connect the IC2 pin to GND.

Remark IC: Internally Connected

$\star$

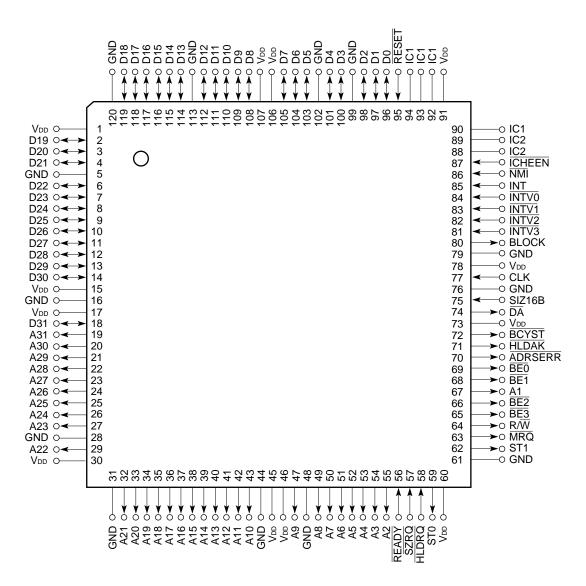

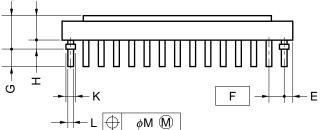

• 120-pin plastic TQFP (Fine pitch) (14 x 14 mm) (Top View) µPD70732GC-25-9EV

- Cautions 1. VDD is power supply pin. All VDD pins should be connected to a +5V power supply (the same power supply).

- 2. GND is ground pin. All GND pins should be connected to the same GND.

- 3. Leave the IC1 pin open.

- 4. Connect the IC2 pin to GND.

Remark IC: Internally Connected

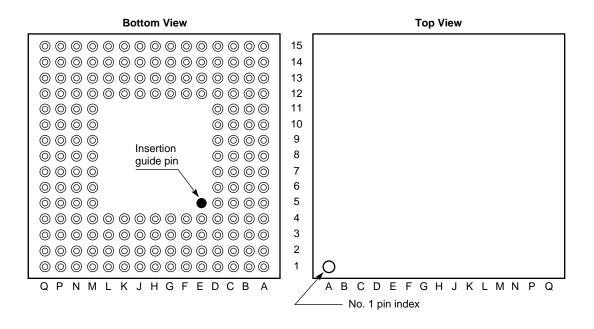

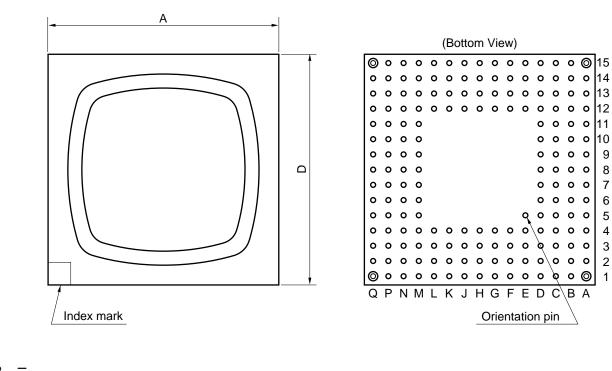

## **176-pin ceramic PGA (Seam weld)** μPD70732R-25

Remark The insertion guide pin is not included in the number of pins.

| No. | Signal | No. | Signal | No. | Signal | No. | Signal       |

|-----|--------|-----|--------|-----|--------|-----|--------------|

| A1  | IC2    | B3  | GND    | C5  | Vdd    | D7  | Vdd          |

| A2  | D12    | B4  | D11    | C6  | D8     | D8  | Vdd          |

| A3  | D13    | B5  | GND    | C7  | Vdd    | D9  | GND          |

| A4  | D10    | B6  | D7     | C8  | D4     | D10 | IC3          |

| A5  | GND    | B7  | Vdd    | C9  | D2     | D11 | IC2          |

| A6  | D6     | B8  | D3     | C10 | IC3    | D12 | GND          |

| A7  | IC2    | B9  | GND    | C11 | Vdd    | D13 | INT          |

| A8  | D5     | B10 | D0     | C12 | IC1    | D14 | INTV1        |

| A9  | IC2    | B11 | GND    | C13 | IC2    | D15 | GND          |

| A10 | D1     | B12 | IC1    | C14 | Vdd    | E1  | D27          |

| A11 | Vdd    | B13 | GND    | C15 | NMI    | E2  | D25          |

| A12 | RESET  | B14 | IC1    | D1  | D23    | E3  | D21          |

| A13 | IC1    | B15 | ICHEEN | D2  | D22    | E4  | D19          |

| A14 | IC1    | C1  | Vdd    | D3  | D20    | E12 | IC3          |

| A15 | IC2    | C2  | Vdd    | D4  | GND    | E13 | <b>INTVO</b> |

| B1  | D17    | C3  | D16    | D5  | D15    | E14 | IC3          |

| B2  | D18    | C4  | D14    | D6  | D9     | E15 | IC1          |

| No. | Signal | No. | Signal | No. | Signal | No. | Signal  |

|-----|--------|-----|--------|-----|--------|-----|---------|

| F1  | Vdd    | J4  | Vdd    | M7  | Vdd    | P4  | A12     |

| F2  | D26    | J12 | IC2    | M8  | A5     | P5  | GND     |

| F3  | D24    | J13 | IC2    | M9  | Vdd    | P6  | A8      |

| F4  | GND    | J14 | IC1    | M10 | ST1    | P7  | GND     |

| F12 | INTV2  | J15 | IC1    | M11 | A1     | P8  | A6      |

| F13 | INTV3  | K1  | IC2    | M12 | GND    | P9  | GND     |

| F14 | Vdd    | K2  | A27    | M13 | BCYST  | P10 | SZRQ    |

| F15 | GND    | К3  | A25    | M14 | DA     | P11 | GND     |

| G1  | D29    | K4  | A24    | M15 | SIZ16B | P12 | MRQ     |

| G2  | D28    | K12 | GND    | N1  | Vdd    | P13 | GND     |

| G3  | IC2    | K13 | BLOCK  | N2  | Vdd    | P14 | ADRSERR |

| G4  | IC2    | K14 | Vdd    | N3  | A17    | P15 | BEO     |

| G12 | Vdd    | K15 | Vdd    | N4  | A15    | Q1  | IC2     |

| G13 | IC2    | L1  | A28    | N5  | Vdd    | Q2  | A13     |

| G14 | IC1    | L2  | A26    | N6  | A9     | Q3  | A14     |

| G15 | IC1    | L3  | A22    | N7  | Vdd    | Q4  | A11     |

| H1  | A31    | L4  | A20    | N8  | Vdd    | Q5  | GND     |

| H2  | D30    | L12 | HLDAK  | N9  | A3     | Q6  | A7      |

| H3  | GND    | L13 | Vdd    | N10 | HLDRQ  | Q7  | IC2     |

| H4  | D31    | L14 | IC1    | N11 | Vdd    | Q8  | A4      |

| H12 | GND    | L15 | IC1    | N12 | BE2    | Q9  | IC2     |

| H13 | CLK    | M1  | GND    | N13 | BE1    | Q10 | A2      |

| H14 | IC1    | M2  | A23    | N14 | Vdd    | Q11 | READY   |

| H15 | IC2    | M3  | A21    | N15 | IC1    | Q12 | ST0     |

| J1  | A30    | M4  | GND    | P1  | A18    | Q13 | BE3     |

| J2  | A29    | M5  | A16    | P2  | A19    | Q14 | R/W     |

| J3  | IC2    | M6  | A10    | P3  | GND    | Q15 | IC2     |

Cautions 1. Leave the IC1 pin open.

- 2. Connect the IC2 pin to GND.

- 3. Connect the IC3 pin to power supply.

Remark IC: Internally Connected

# CONTENTS

| 1.                                   | 1. PIN FUNCTIONS           |                                          |    |   |  |  |

|--------------------------------------|----------------------------|------------------------------------------|----|---|--|--|

|                                      |                            |                                          |    |   |  |  |

|                                      | 1.2 Pin I/O Circuits and R | Recommended Connection of Unused Pins    | 10 | * |  |  |

| 2.                                   | . REGISTER SET             |                                          | 12 | * |  |  |

|                                      | 2.1 Program Register Set   |                                          | 13 |   |  |  |

|                                      | 2.2 System Register Set .  |                                          | 14 |   |  |  |

| 3.                                   | . DATA TYPES               |                                          | 15 | * |  |  |

|                                      | 3.1 Data Types             |                                          | 15 |   |  |  |

|                                      | 3.1.1 Data type and ad     | ldressing                                | 15 |   |  |  |

|                                      | 3.1.2 Integer              |                                          | 16 |   |  |  |

|                                      | 3.1.3 Unsigned integer     |                                          | 16 |   |  |  |

|                                      | 3.1.4 Bit string           |                                          | 16 |   |  |  |

|                                      | 3.1.5 Single-precision f   | loating-point data                       | 17 |   |  |  |

|                                      | 3.2 Data Alignment         |                                          |    |   |  |  |

| 4.                                   | . ADDRESS SPACE            |                                          | 18 | * |  |  |

| 5.                                   | . BUS INTERFACE FUNCTIO    | Ν                                        | 21 | * |  |  |

| •                                    |                            |                                          |    | ~ |  |  |

| 6.                                   | . INTERRUPT AND EXCEPTION  | ON                                       | 22 | * |  |  |

| 7.                                   | . CACHE                    |                                          | 23 | * |  |  |

| 8.                                   | . RESET                    |                                          | 24 | * |  |  |

| 9.                                   | . INSTRUCTION SET          |                                          | 25 | * |  |  |

|                                      | 9.1 Instruction Format     |                                          | 25 |   |  |  |

|                                      | 9.2 Instruction Mnemonic   | : (in alphabetical order)                | 27 |   |  |  |

| 10.                                  | 0. ELECTRICAL SPECIFICATI  | ONS                                      | 37 |   |  |  |

|                                      | 10.1 Specifications When   | $V_{DD} = +5 V \pm 10\%$                 | 38 |   |  |  |

|                                      | 10.2 Specifications When   | VDD = 2.7 to 3.6 V                       | 47 |   |  |  |

|                                      | 10.3 Specifications When   | $V_{DD} = 2.2 \text{ to } 3.6 \text{ V}$ | 51 |   |  |  |

| 11. PACKAGE DRAWINGS                 |                            |                                          |    |   |  |  |

| 12. RECOMMENDED SOLDERING CONDITIONS |                            |                                          |    |   |  |  |

# 1. PIN FUNCTIONS

## 1.1 Pin Function List

| Name                                 | I/O               | Function                                           | Bus hold<br>status<br>during<br>operation | Bus hold<br>status<br>at reset | Bus idle<br>status<br>at reset |

|--------------------------------------|-------------------|----------------------------------------------------|-------------------------------------------|--------------------------------|--------------------------------|

| A31 to A1<br>(Address Bus)           | 3-state<br>output | Address bus                                        | Hi-Z                                      | Hi-Z                           | H <sup>Note</sup>              |

| D31 to D0<br>(Data Bus)              | 3-state<br>I/O    | Bidirectional data bus                             | Hi-Z                                      | Hi-Z                           | Hi-Z                           |

| BE3 to BE0<br>(Byte Enable)          | 3-state<br>output | Indicates valid data bus when data is accessed     | Hi-Z                                      | Hi-Z                           | Н                              |

| ST1, ST0<br>(Status)                 | 3-state<br>output | Indicates type of bus cycle                        | Hi-Z                                      | Hi-Z                           | Н                              |

| DA<br>(Data Access)                  | 3-state<br>output | Strobe signal for bus cycle                        | Hi-Z                                      | Hi-Z                           | Н                              |

| MRQ<br>(Memory Request)              | 3-state<br>output | Indicates memory access                            | Hi-Z                                      | Hi-Z                           | Н                              |

| R/₩<br>(Read/Write)                  | 3-state<br>output | Distinguishes between read access and write access | Hi-Z                                      | Hi-Z                           | Н                              |

| BCYST<br>(Bus Cycle Start)           | 3-state<br>output | Indicates start of bus cycle                       | Hi-Z                                      | Hi-Z                           | н                              |

| READY<br>(Ready)                     | Input             | Extends bus cycle                                  | _                                         | _                              | _                              |

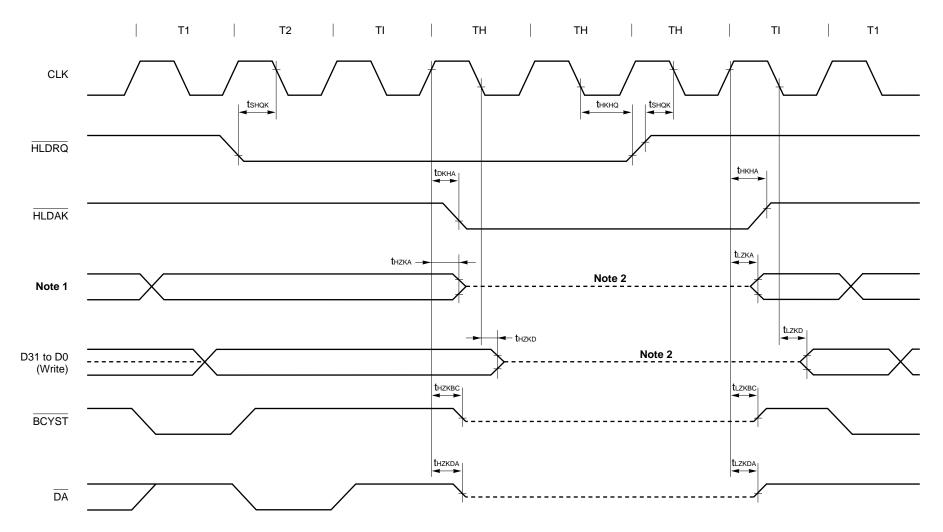

| HLDRQ<br>(Hold Request)              | Input             | Requests bus mastership                            | _                                         | _                              | _                              |

| HLDAK<br>(Hold Acknowledge)          | Output            | Acknowledges HLDRQ                                 | L                                         | L                              | Н                              |

| SZRQ<br>(Bus Sizing Request)         | Input             | Requests bus sizing                                | _                                         | _                              | _                              |

| SIZ16B<br>(Bus Size 16 Bit)          | Input             | Fixes external data bus width to 16 bits           | _                                         | _                              | _                              |

| BLOCK<br>(Bus Lock)                  | Output            | Requests to inhibit use of bus                     | L                                         | L                              | L                              |

| ICHEEN<br>(Instruction Cache Enable) | Input             | Operates instruction cache                         | -                                         | _                              | _                              |

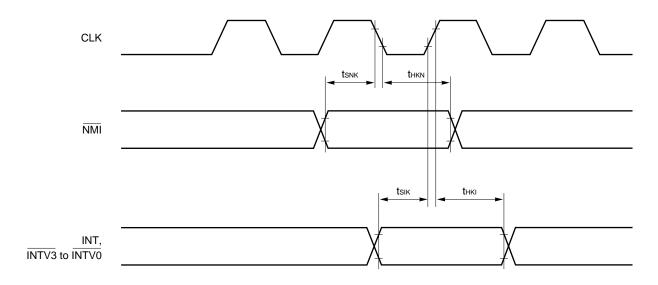

| INT<br>(Maskable Interrupt)          | Input             | Interrupt request                                  | _                                         | _                              | _                              |

| INTV3 to INTV0<br>(Interrupt Level)  | Input             | Interrupt level                                    | —                                         | —                              | —                              |

Note A1 pin is "H" in the 16-bit bus fixed mode; otherwise, it is "L".

| Name                            | I/O    | Function                                                 | Bus hold<br>status<br>during<br>operation | Bus hold<br>status<br>at reset | Bus idle<br>status<br>at reset |

|---------------------------------|--------|----------------------------------------------------------|-------------------------------------------|--------------------------------|--------------------------------|

| NMI<br>(Non-Maskable Interrupt) | Input  | Non-maskable interrupt request                           | _                                         | _                              | _                              |

| CLK                             | Input  | CPU clock input                                          | _                                         | _                              | _                              |

| RESET<br>(Reset)                | Input  | Resets internal status                                   | _                                         | _                              | _                              |

| ADRSERR<br>(Address Error)      | Output | Indicates that data alignment is illegal                 | Not<br>affected                           | Н                              | Н                              |

| VDD<br>(Power Supply)           | _      | Positive power supply                                    | _                                         | _                              | _                              |

| GND<br>(Ground)                 | _      | Ground potential (0 V)                                   | _                                         | _                              | _                              |

| IC1<br>(Internally Connected 1) | _      | Internally connected (Leave this pin open.)              | _                                         | _                              | _                              |

| IC2<br>(Internally Connected 2) | _      | Internally connected (Ground this pin.)                  | _                                         | _                              | —                              |

| IC3<br>(Internally Connected 3) | —      | Internally connected (Connect this pin to power supply.) | —                                         | —                              |                                |

\_\_\_\_\_

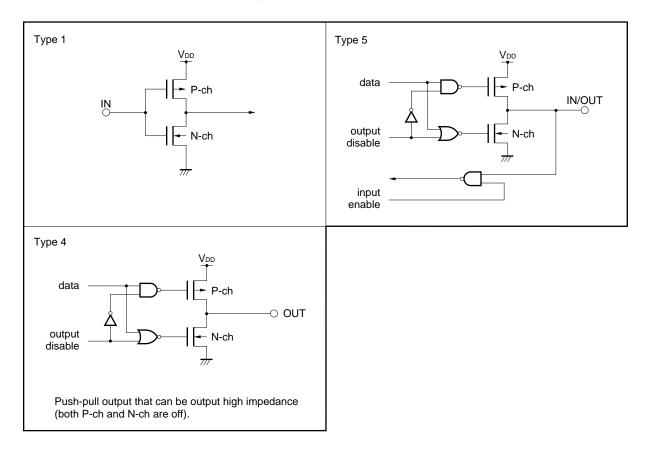

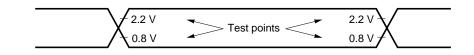

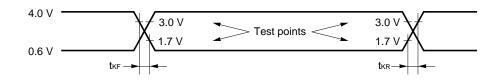

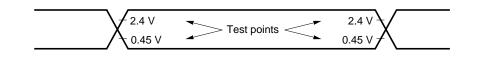

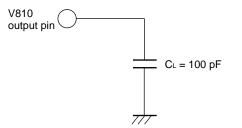

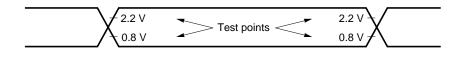

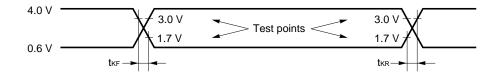

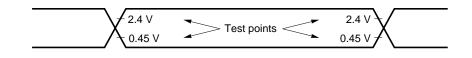

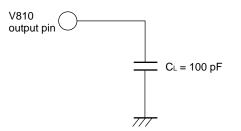

# ★ 1.2 Pin I/O Circuits and Recommended Connection of Unused Pins

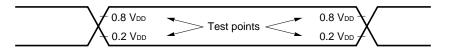

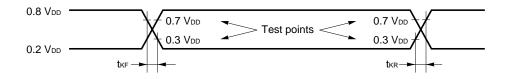

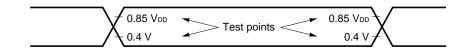

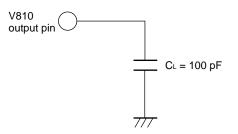

The I/O circuit type of each pin and recommended connection of unused pins are shown in Table 1-1. Figure 1-1 shows the I/O circuit of each type.

| Pin            | I/O Circuit Type | Recommended Connection Method |

|----------------|------------------|-------------------------------|

| D31 to D0      | 5                | Open                          |

| A31 to A1      | 4                |                               |

| BE3 to BE0     |                  |                               |

| ST1, ST0       |                  |                               |

| DA             | -                |                               |

| MRQ            |                  |                               |

| R/W            | -                |                               |

| BCYST          | -                |                               |

| READY          | 1                | Connect to GND via resistor   |

| HLDRQ          |                  | Connect to VDD via resistor   |

| HLDAK          | 4                | Open                          |

| SZRQ           | 1                | Connect to VDD via resistor   |

| SIZ16B         |                  | Connect to GND via resistor   |

| BLOCK          | 4                | Open                          |

| ICHEEN         | 1                | Connect to VDD via resistor   |

| INT            |                  | Connect to GND via resistor   |

| INTV3 to INTV0 |                  | Connect to VDD via resistor   |

| NMI            |                  |                               |

| CLK            |                  | —                             |

| RESET          |                  |                               |

| ADRSERR        | 4                | Open                          |

| IC1            |                  |                               |

| IC2            | —                | Connect to GND                |

| IC3            | _                | Connect to VDD                |

### Table 1-1. Pin I/O Circuit Types and Recommended Connection Method of Unused Pins

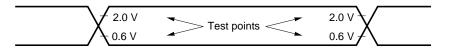

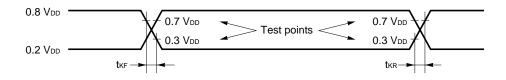

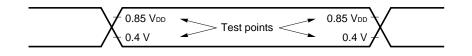

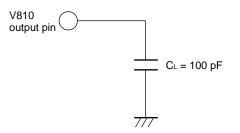

Figure 1-1. Pin I/O Circuit

# NEC

# ★ 2. REGISTER SET

The registers of the V810 can be classified into two types: general-purpose program register set and dedicated system register set. All registers are 32 bits wide.

|     | Program register sets           |   |

|-----|---------------------------------|---|

| 31  |                                 | 0 |

| r0  | Zero Register                   |   |

| r1  | Reserved for Address Generation |   |

| r2  | Handler Stack Pointer (hp)      |   |

| r3  | Stack Pointer (sp)              |   |

| r4  | Global Pointer (gp)             |   |

| r5  | Text Pointer (tp)               |   |

| r6  |                                 |   |

| r7  |                                 |   |

| r8  |                                 |   |

| r9  |                                 |   |

| r10 |                                 |   |

| r11 |                                 |   |

| r12 |                                 |   |

| r13 |                                 |   |

| r14 |                                 |   |

| r15 |                                 |   |

| r16 |                                 |   |

| r17 |                                 |   |

| r18 |                                 |   |

| r19 |                                 |   |

| r20 |                                 |   |

| r21 |                                 |   |

| r22 |                                 |   |

| r23 |                                 |   |

| r24 |                                 |   |

| r25 |                                 |   |

| r26 | String Destination Bit Offset   |   |

| r27 | String Source Bit Offset        |   |

| r28 | String Length                   |   |

| r29 | String Destination              |   |

| r30 | String Source                   |   |

| r31 | Link Pointer (lp)               |   |

|     |                                 |   |

#### System register sets

| 31    |                         | 0 |

|-------|-------------------------|---|

| EIPC  | Exception/Interrupt PC  |   |

| EIPSW | Exception/Interrupt PSW |   |

| 31    | 0               |

|-------|-----------------|

| FEPC  | Fatal Error PC  |

| FEPSW | Fatal Error PSW |

| 31  |                          |

|-----|--------------------------|

| ECR | Exception Cause Register |

0

| 31  |                     | 0 |

|-----|---------------------|---|

| PSW | Program Status Word |   |

| 31  |                       | 0 |

|-----|-----------------------|---|

| PIR | Processor ID Register |   |

| 31   |                   | 0 |

|------|-------------------|---|

| TKCW | Task Control Word |   |

31 0 CHCW Cache Control Word

| 31 | 1     |                       | 0 |

|----|-------|-----------------------|---|

|    | ADTRE | Address Trap Register |   |

31

| PC | Program Counter |  |

|----|-----------------|--|

0

#### 2.1 Program Register Set

The program register set is composed of general-purpose registers and a program counter.

#### (1) General-purpose registers

Thirty-two general-purpose registers, r0 to r31, are available. All these registers can be used as data registers or address registers.

Of these registers, r0 and r26 through r30 are implicitly used by some instructions, and r1 through r5 and r31 are implicitly used by the assembler and C compiler. Therefore, when using these registers, it is necessary to take special care such as saving these registers' contents to different areas before using these registers and restoring the contents after using them.

| Register  | Application                         | Operation                                                       |

|-----------|-------------------------------------|-----------------------------------------------------------------|

| rO        | Zero register                       | Always holds zeros.                                             |

| r1        | Register reserved for assembler     | Used as a working register to generate a 32-bit immediate data. |

| r2        | Handler stack pointer               | Used as the stack pointer for the handler.                      |

| r3        | Stack pointer                       | Used to generate a stack frame at a function call.              |

| r4        | Global pointer                      | Used to access a global variable in the data area.              |

| r5        | Text pointer                        | Points the start address of the text area.                      |

| r6 to r25 | _                                   | Stores address or data variables.                               |

| r26       | String destination bit offset       | Used in a bit-string instruction execution.                     |

| r27       | String source bit offset            |                                                                 |

| r28       | String length register              |                                                                 |

| r29       | String destination address register |                                                                 |

| r30       | String address register             |                                                                 |

| r31       | Link pointer                        | Stores the return address at execution of a JAL instruction.    |

Table 2-1. Program Registers

#### (2) Program Counter

The program counter (PC) indicates the address of the instruction currently executed by the program. Bit 0 of the PC is fixed to 0, and execution cannot branch to an odd address. The contents of the PC are initialized to FFFFFF0H at reset.

#### 2.2 System Register Set

The system register set is composed of the following registers that perform operations such as CPU-status control and interrupt information holding.

| Number   | Register Name | Application                                     | Operation                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|----------|---------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0        | EIPC          | Status saving registers for exception/interrupt | The EIPC and EIPSW registers save the PC and PSW, respectively, when an exception or interrupt occurs. Because in the V810 the registers incorporated for this purpose are                                                                                                                                                |  |  |  |  |

| 1        | EIPSW         |                                                 | these registers only, save the contents of these registers by means<br>of programming if your application set can cause multiple interrupt<br>requests to be issued in the V810.                                                                                                                                          |  |  |  |  |

| 2        | FEPC          | Status saving registers for                     | The FEPC and FEPSW registers save the PC and PSW,                                                                                                                                                                                                                                                                         |  |  |  |  |

| 3        | FEPSW         | NMI/duplexed exception                          | respectively, when an NMI or duplexed exception occurs.                                                                                                                                                                                                                                                                   |  |  |  |  |

| 4        | ECR           | Exception cause register                        | This register, when an exception, maskable interrupt, or NMI occurs, holds its cause. This register consists of 32 bits. Its higher 16 bits, called FECC, hold the exception code for an NMI or duplexed exception, while the lower 16 bits, called EICC, hold the exception code for an exception or maskable interrupt. |  |  |  |  |

| 5        | PSW           | Program status word                             | This register, also called the program status word, is a set of flags indicating the statuses of the CPU and program (instruction execution results).                                                                                                                                                                     |  |  |  |  |

| 6        | PIR           | Processor ID register                           | This register identifies the CPU type number.                                                                                                                                                                                                                                                                             |  |  |  |  |

| 7        | TKCW          | Task control word                               | This register controls floating-point operations.                                                                                                                                                                                                                                                                         |  |  |  |  |

| 8 to 23  | Reserved      |                                                 |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 24       | CHCW          | Cache control word                              | This register controls the on-chip instruction cache.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 25       | ADTRE         | Address trap register                           | This register holds an address and is used for address trapping.<br>When the address in this register matches the PC value, the<br>execution jumps to a predefined address.                                                                                                                                               |  |  |  |  |

| 26 to 31 | Reserved      |                                                 |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Table | 2-2. | System | Register | Number    |

|-------|------|--------|----------|-----------|

|       |      | 0,000  | g.o.o.   | 110111001 |

To read or write one of the registers shown above, specify a system register number with the system register load (LDSR) or system register store (STSR) instruction.

$\star$

#### 3. DATA TYPES

#### 3.1 Data Types

The data types supported by the V810 are as follows:

- Integer (8, 16, 32 bits)

- Unsigned integer (8, 16, 32 bits)

- Bit string

- Single-precision floating-point data (32 bits)

#### 3.1.1 Data type and addressing

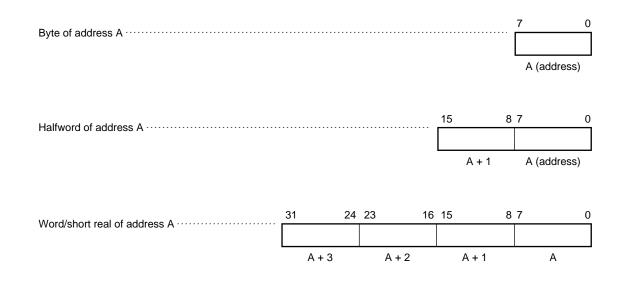

The V810 uses the little-endian data addressing. In this addressing, if a fixed-length data is located in a memory area, the data must be either of the data types shown below.

#### (1) Byte

A byte is a consecutive 8-bit data whose first-bit address is aligned to a byte boundary. Each bit in a byte is numbered from 0 to 7: LSB (the least significant bit) is bit 0 and MSB (the most significant bit) is bit 7. To access a byte, specify address A. (See diagram below.)

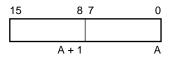

#### (2) Halfword

A halfword is a consecutive 16-bit (= 2 bytes) data whose first-bit address is aligned to a halfword boundary. Each bit in a halfword is numbered from 0 to 15: LSB (the least significant bit) is bit 0 and MSB (the most significant bit) is bit 15. To access a halfword, specify the address A only (lowest bit must be 0).

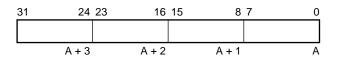

#### (3) Word/short real

A word, also called short real, is a consecutive 32-bit (= 4 bytes) data whose first-bit address is aligned to a word boundary. Each bit in a word is numbered from 0 to 31: LSB (the least significant bit) is bit 0 and MSB (the most significant bit) is bit 31. To access a word or short real, specify the address A only (lower two bits must be 0).

# NEC

## 3.1.2 Integer

In the V810, all integers are expressed in the two's-complement binary notation, and are composed of either 8 bits, 16 bits, or 32 bits. Regardless of the data length, bit 0 is the least significant bit, and higher-numbered bits express higher digits of the integer with the highest bit expressing its sign.

| Data        | Length  | Range                      |

|-------------|---------|----------------------------|

| Byte 8 bits |         | -128 to +127               |

| Halfword    | 16 bits | -32768 to +32767           |

| Word        | 32 bits | -2147483648 to +2147483647 |

#### 3.1.3 Unsigned integer

An unsigned integer is either zero or a positive integer unlike the integer explained in section 3.1.2 which can be negative as well as zero and positive. Unsigned integers are expressed in the binary notation in the same way as integers, and are either 8 bits, 16 bits, or 32 bits long. Regardless of the data length, the bit assignments are the same as in the case of integers except that unsigned integers do not include a sign bit; the highest bit is also a part of the integer.

| Data     | Length  | Range           |  |  |  |

|----------|---------|-----------------|--|--|--|

| Byte     | 8 bits  | 0 to 255        |  |  |  |

| Halfword | 16 bits | 0 to 65535      |  |  |  |

| Word     | 32 bits | 0 to 4294967295 |  |  |  |

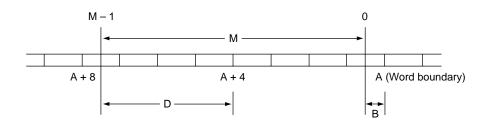

## 3.1.4 Bit string

A bit string is a type of data whose bit length is variable from 0 to  $2^{32} - 1$ . To specify a bit-string data, define the following three attributes.

- A : address of the string data's first word (lower two bits must be 0.)

- B : in-word bit offset in the string data (0 to 31)

- M : bit length of the string data (0 to  $2^{32} 1$ )

The above three attributes may vary depending on the bit-string data manipulation direction: upward or downward, as shown below. The former is the direction from lower addresses to higher addresses while the latter is the direction from higher to lower addresses.

| Attribute                               | Upward | Downward |

|-----------------------------------------|--------|----------|

| First-word address (0s in bits 1 and 0) | A      | A + 4    |

| In-word bit offset (0 to 31)            | В      | D        |

| Bit length (0 to 2 <sup>32</sup> – 1)   | М      | М        |

#### 3.1.5 Single-precision floating-point data

This data type is 32 bits long and its bit allocation complies with the IEEE single format. A single-precision floating-point data consists of 1-bit mantissa sign bit, 8-bit exponent, and 23-bit mantissa. The exponent is offset-expressed from the bias value -127, and the mantissa is binary-expressed with the integer part omitted.

| 31 | 30 | 23      | 22 0          |

|----|----|---------|---------------|

| s  |    | exp (8) | mantissa (23) |

#### 3.2 Data Alignment

In the V810, a word data must be aligned to a word boundary (with the lowest two bits of the address fixed to 0s), and a halfword data to a halfword boundary (with the lowest bit of the address fixed to 0). If a data is not aligned as specified, the lowest one bit (in the case of word) or two bits (in the case of halfword) of its address will forcibly be masked with 0s when the data is accessed.

#### ★ 4. ADDRESS SPACE

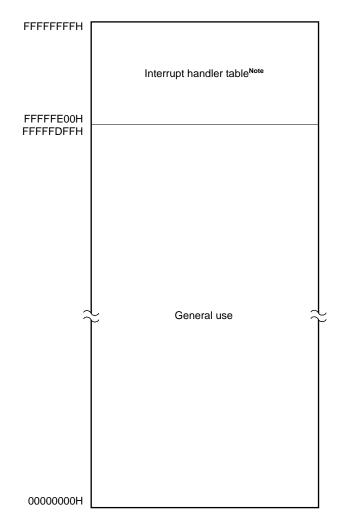

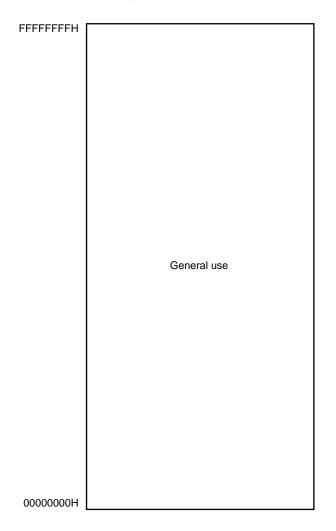

The V810 supports 4 Gbytes of linear memory space and I/O space. The CPU outputs 32-bit addresses to the memory and I/Os; therefore, the addresses are from 0 to  $2^{32} - 1$ .

Bit number 0 of each byte data is defined as the LSB (Least Significant Bit), and bit number 7 is the MSB (Most Significant Bit). Unless otherwise specified, the byte data at the lower address side of data consisting of two or more bytes is the LSB, and the byte data at the higher address side is the MSB (little endian).

Data consisting of 2 bytes is called a halfword, and data consisting of 4 bytes is called a word. The lower address of memory or I/O data of two or more bytes, here, is shown on the right, and the higher address is shown on the left, as follows:

Figure 4-1 shows the memory map of the V810, and Figure 4-2 shows the I/O map.

Figure 4-1. Memory Map

Note For the details, refer to Table 6-1 Exception Codes.

Figure 4-2. I/O Map

★

#### 5. BUS INTERFACE FUNCTION

The V810 is equipped with a 32-bit data bus.

In the bus interface, there are two modes: 32-bit bus mode which uses the data bus in 32 bits and 16-bit bus fixed mode which fixes the bus in 16 bits. Modes can be switched only at reset using the SIZ16B signal.

The 32-bit bus mode has a dynamic bus sizing function which uses the data bus in 16-bit bus width to access the 16-bit peripherals. This function can be used by setting the  $\overline{SZRQ}$  signal active. Access to word data (32-bit data) in the dynamic bus sizing is executed by loading/storing a 16-bit data twice.

In the 16-bit bus fixed mode, access to word data (32-bit data) is executed by activating a bus cycle twice. The control signal and the A1 signal output values according to the 16-bit system.

The relationship between the external access and byte enable signals ( $\overline{BE3}$  to  $\overline{BE0}$ ) during the 32-bit bus mode and the 16-bit bus fixed mode is shown below.

| Data longth | Operand address |       | Byte enable |     |     |     |    | Bus cycle         |

|-------------|-----------------|-------|-------------|-----|-----|-----|----|-------------------|

| Data length | Bit 1           | Bit 0 | BE3         | BE2 | BE1 | BE0 | A1 | sequence          |

| Byte        | 0               | 0     | 1           | 1   | 1   | 0   | 0  | 1                 |

|             | 0               | 1     | 1           | 1   | 0   | 1   | 0  | 1                 |

|             | 1               | 0     | 1           | 0   | 1   | 1   | 0  | 1                 |

|             | 1               | 1     | 0           | 1   | 1   | 1   | 0  | 1                 |

| Halfword    | 0               | 0     | 1           | 1   | 0   | 0   | 0  | 1                 |

|             | 1               | 0     | 0           | 0   | 1   | 1   | 0  | 1                 |

| Word        | 0               | 0     | 0           | 0   | 0   | 0   | 0  | 1                 |

|             |                 |       | 0           | 0   | 1   | 1   | 1  | 2 <sup>Note</sup> |

# Table 5-1. Relationship among Address, Data Length, Byte Enable Signals and A1 (32-bit bus mode)

Note Bus cycle added by dynamic bus sizing

# Table 5-2. Relationship among Address, Data Length, Byte Enable Signals and A1 (16-bit bus fixed mode)

| Data longth | Operand | address |      | Byte e | enable |     |    | Bus cycle         |

|-------------|---------|---------|------|--------|--------|-----|----|-------------------|

| Data length | Bit 1   | Bit 0   | BE3  | BE2    | BE1    | BE0 | A1 | sequence          |

| Byte        | 0       | 0       | Hi-Z | Hi-Z   | 1      | 0   | 0  | 1                 |

|             | 0       | 1       | Hi-Z | Hi-Z   | 0      | 1   | 0  | 1                 |

|             | 1       | 0       | Hi-Z | Hi-Z   | 1      | 0   | 1  | 1                 |

|             | 1       | 1       | Hi-Z | Hi-Z   | 0      | 1   | 1  | 1                 |

| Halfword    | 0       | 0       | Hi-Z | Hi-Z   | 0      | 0   | 0  | 1                 |

|             | 1       | 0       | Hi-Z | Hi-Z   | 0      | 0   | 1  | 1                 |

| Word        | 0       | 0       | Hi-Z | Hi-Z   | 0      | 0   | 0  | 1                 |

|             |         |         | Hi-Z | Hi-Z   | 0      | 0   | 1  | 2 <sup>Note</sup> |

**Note** Added bus cycle

#### ★ 6. INTERRUPT AND EXCEPTION

Interrupts are events that take place independently of the program execution and can be classified into maskable interrupts and a non-maskable interrupt. An exception is an event that takes place depending upon the program execution. There is little difference between the interrupt and exception in terms of flow, but the interrupt takes precedence over the exception.

The V810 architecture is provided with the interrupts and exceptions listed in the table below. If an exception, a maskable interrupt or NMI occurs, control is transferred to a handler whose address is determined by the source of the interrupt or exception. The exception source can be checked by examining an exception code stored in the ECR (Exception Code Register). Each handler analyzes the contents of the ECR and performs appropriate exception/interrupt servicing.

| Exception and interrupt                          | Classification | Exception code | Handler address | Restore PC <sup>Note 1</sup> |

|--------------------------------------------------|----------------|----------------|-----------------|------------------------------|

| Reset                                            | Interrupt      | F F F O        | FFFFFFF0        | Note 2                       |

| NMI                                              | Interrupt      | F F D O        | FFFFFD0         | next PC <sup>Note 3</sup>    |

| Duplexed exception                               | Exception      | Note 4         | FFFFFD0         | current PC                   |

| Address trap                                     | Exception      | FFC0           | FFFFFFC0        | current PC                   |

| Trap instruction (parameter is 0x1n)             | Exception      | FFBn           | FFFFFB0         | next PC                      |

| Trap instruction (parameter is 0x0n)             | Exception      | FFAn           | FFFFFFA0        | next PC                      |

| Invalid instruction code                         | Exception      | F F 9 0        | FFFFFF90        | current PC                   |

| Zero division                                    | Exception      | F F 8 0        | FFFFFF80        | current PC                   |

| FIV (floating-point invalid operation)           | Exception      | F F 7 0        | FFFFFF60        | current PC                   |

| FZD (floating-point zero division)               | Exception      | F F 6 8        | FFFFFF60        | current PC                   |

| FOV (floating-point overflow)                    | Exception      | F F 6 4        | FFFFFF60        | current PC                   |

| FUD (floating-point underflow) <sup>Note 5</sup> | Exception      | F F 6 2        | FFFFFF60        | current PC                   |

| FPR (floating-point precision degradation)Note 5 | Exception      | F F 6 1        | FFFFFF60        | current PC                   |

| FRO (floating-point reserved operand)            | Exception      | F F 6 0        | FFFFFF60        | current PC                   |

| INT level n (n = 0 to 15)                        | Interrupt      | FEn0           | FFFFFEn0        | next PC <sup>Note 3</sup>    |

| Table | 6-1. | Exception | Codes |

|-------|------|-----------|-------|

|-------|------|-----------|-------|

Notes 1. PC to be saved to EIPC or FEPC.

- 2. EIPC and FEPC are undefined.

- While an instruction whose execution is aborted by an interrupt (DIV/DIVU, single-precision floatingpoint data, bit string instruction) is executed, restore PC = current PC.

- **4.** The exception code of the exception that occurs for the first time is stored to the lower 16 bits of the ECR, and that of the second exception is stored in the higher 16 bits.

- 5. In the V810, the floating-point underflow exception and floating-point precision degradation exception do not occur.

$\star$

# 7. CACHE

Figure 7-1 shows the instruction cache configuration provided to the V810.

Figure 7-1. Cache Configuration

# NEC

## ★ 8. RESET

A low-level input detection on the RESET pin always triggers a system reset. Consequently, all the hardwarecontrolling registers are initialized as shown in Table 8-1. After the initialization procedure is completed and the RESET pin returns to the high level, the device is released from the resetting state and starts the implementation of a program. Then, if necessary, set some registers to user-desired values in the first stage of the program.

| Hardware (Symbol)                    |           | State after Reset  |

|--------------------------------------|-----------|--------------------|

| Program counter                      | PC        | FFFFFF0H           |

| Status saving register for interrupt | EIPC      | Undefind           |

|                                      | EIPSW     | -                  |

| Status saving register for NMI       | FEPC      | Undefind           |

|                                      | FEPSW     | -                  |

| Interrupt cause register             | FECC      | 0000H              |

|                                      | EICC      | FFF0H              |

| Program status word                  | PSW       | 00008000H          |

| General-purpose register             | r0        | Fixed to 00000000H |

|                                      | r1 to r31 | Undefind           |

| Table 8-1. Register State after Rese |

|--------------------------------------|

|--------------------------------------|

#### 9. INSTRUCTION SET

#### 9.1 Instruction Format

The V810 instructions are formatted in either 16 bits or 32 bits. Examples of the 16-bit format instruction are binomial operation, control, and conditional branch; those for the 32-bit format are load/store, I/O manipulate, 16-bit immediate, jump & link, and extended operations.

Some instructions have an unused field. However, do not write a program that uses this field because it is reserved for future use. This unused field must be set to zeros.

Instructions are stored in memory in the following manner.

- The lower half of an instruction, that is, the half which includes bit 0, is stored at the lower address.

- The higher half of an instruction, that is, the half which includes bit 15 or 31, is stored at the higher address.

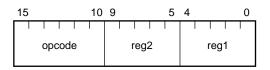

#### (1) reg-reg instruction format (Format I)

This format consists of one 6-bit field to hold an operation code and two 5-bit fields to specify generalpurpose registers as instruction's operands. 16-bit instructions use this format.

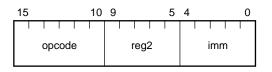

#### (2) imm-reg instruction format (Format II)

This format consists of one 6-bit field to hold an operation code, one 5-bit field to hold an immediate data, and one field to specify a general-purpose register as an operand. 16-bit instructions use this format.

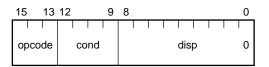

#### (3) Conditonal branch instruction format (Format III)

This format consists of one 3-bit field to hold an operation code, one 4-bit field to hold a condition code, and one 9-bit field to hold a branch displacement (with its LSB masked to 0). 16-bit instructions use this format.

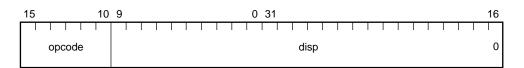

#### (4) Intermediate jump instruction format (Format IV)

This format consists of one 6-bit field to hold an operation code and one 26-bit field to hold a displacement (with its LSB masked to 0). 32-bit instructions use this format.

#### (5) 3-operand instruction format (Format V)

This format consists of one 6-bit field to hold an operation code, two fields to specify general-purpose registers as operands, and one 16-bit field to hold an immediate data. 32-bit instructions use this format.

| 15 |    |    |    | 10 | 9 |   |    |    | 5 | 2 | 4 |    |    | ( | ) 3 | 31 |  |  |   |    |   |   |   |  |   |   | 16 |

|----|----|----|----|----|---|---|----|----|---|---|---|----|----|---|-----|----|--|--|---|----|---|---|---|--|---|---|----|

|    | I  | I  |    | I  |   | I | Ι  | I  | I |   | Ι | I  |    |   |     | I  |  |  | I |    |   | I | Ι |  | I | I |    |

|    | ор | co | de |    |   |   | re | g2 |   |   |   | re | g1 |   |     |    |  |  |   | im | m |   |   |  |   |   |    |

#### (6) Load/store instruction format (Format VI)

This format consists of one 6-bit field to hold an operation code, two fields to specify a general-purpose register, and one 16-bit field to hold a displacement. 32-bit instructions use this format.

| 15 |   |   |    |   | 10 | 9 | ) |    |    | ; | 5 | 4 |     |    | 0 | 31 |  |  |   |  |   |      |   |  |   |   | 16 |  |

|----|---|---|----|---|----|---|---|----|----|---|---|---|-----|----|---|----|--|--|---|--|---|------|---|--|---|---|----|--|

|    | Ι |   |    | I |    |   |   |    |    |   |   |   |     |    |   |    |  |  | I |  |   |      | Ι |  | Ι | I |    |  |

|    | o | C | bd | е |    |   |   | re | g2 |   |   |   | reg | g1 |   |    |  |  |   |  | C | lisp | ) |  |   |   |    |  |

#### (7) Extension instruction format (Format VII)

This format consists of one 6-bit field to hold an operation code, two 5-bit fields to specify general-purpose registers as operands, and one 6-bit field to hold an sub-operation code. The remaining 10 bits are reserved for future use and must be set to zeros. 32-bit instructions use this format.

|   | 15 |         |         | 10 | 9 |    |    | 5 | 4 |    |     | 0 | 31 |    |          |     |          |        |  |   |   |          |   |  | 16 |

|---|----|---------|---------|----|---|----|----|---|---|----|-----|---|----|----|----------|-----|----------|--------|--|---|---|----------|---|--|----|

| ſ |    | l<br>op | l<br>de |    |   | re | g2 |   |   | re | :g1 | I |    | su | l<br>b-o | pcc | l<br>ode | )<br>Ə |  | I | I | ।<br>RFI | J |  |    |

|   |    | - 1     |         |    |   |    | 5  |   |   | -  | 5   |   |    |    |          |     |          | _      |  |   |   |          | - |  |    |

#### 9.2 Instruction Mnemonic (in alphabetical order)

The list of mnemonics is shown below.

This section lists the instructions incorporated in the V810 along with their operations. The instructions are listed in the instruction mnemonic's alphabetical order to allow users to use this section as a quick reference or dictionary. The conventions used in the list are shown below.

| Instruction Mnem   | nonic  | Operand (s)           | Format                                        | CY OV S Z Instruction Function        |

|--------------------|--------|-----------------------|-----------------------------------------------|---------------------------------------|

| egend              |        |                       |                                               |                                       |

| ADD                |        | reg1, reg2            | I                                             | * * * *                               |

| Ļ                  |        | Ļ                     | L L                                           | <b>V</b>                              |

| Mnemonic of instru | uction | Identifier of operand | Instruction format<br>(Refer to <b>9.1</b> .) | Flag operation                        |

|                    |        |                       |                                               | <ul> <li>Remains unchanged</li> </ul> |

|                    |        |                       |                                               | * Inverts the previous value          |

|                    |        |                       |                                               | 0 Changes to 0                        |

|                    |        |                       |                                               | 1 Changes to 1                        |

|                    |        |                       |                                               |                                       |

| Identifier         |        |                       | Description                                   |                                       |

| rog1 Cr            |        | radiator (Llaad aa    |                                               |                                       |

| Identifier | Description                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------|

| reg1       | General-purpose register (Used as a source register)                                                   |

| reg2       | General-purpose register (Used mainly as a destination register and occasionally as a source register) |

| imm5       | 5-bit immediate                                                                                        |

| imm16      | 16-bit immediate                                                                                       |

| disp9      | 9-bit displacement                                                                                     |

| disp16     | 16-bit displacement                                                                                    |

| disp26     | 26-bit displacement                                                                                    |

| regID      | System register number                                                                                 |

| vector adr | Trap handler address that corresponds to a trap vector                                                 |

| Instruction | Operand (s)       | Format | CY | ٥V | S | Z | Instruction Function                                                                                                                                                                                                                                                                                     |

|-------------|-------------------|--------|----|----|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic    |                   |        |    |    |   |   |                                                                                                                                                                                                                                                                                                          |

| ADD         | reg1, reg2        | I      | *  | *  | * | * | Addition:<br>Adds the word data in the reg2-specified register and<br>the word data in the reg1-specified register, the<br>stores the result into the reg2-specified register.                                                                                                                           |

| ADD         | imm5, reg2        | ΙΙ     | *  | *  | * | * | Addition:<br>Sign-extends the 5-bit immediate data to 32 bits, and<br>adds the extended immediate data and the word data<br>in the reg2-specified register, then stores the resu<br>into the reg2-specified register.                                                                                    |

| ADDF.S      | reg1, reg2        | VII    | *  | 0  | * | * | Floating-point addition:<br>Adds the single-precision floating-point data in the<br>reg2-specified register and the single-precision floating<br>point data in the reg1-specified register, then restore<br>the result into the reg2-specified register while changing<br>flags according to the result. |

| ADDI        | imm16, reg1, reg2 | V      | *  | *  | * | * | Addition:<br>Sign-extends the 16-bit immediate data to 32 bits, and<br>adds the extended immediate data and the word data<br>in the reg1-specified register, then stores the resu<br>into the reg2-specified register.                                                                                   |

| AND         | reg1, reg2        | I      | _  | 0  | * | * | AND:<br>Performs the logical AND operation on the word dat<br>in the reg2-specified register and the word data in th<br>reg1-specified register, then stores the result into th<br>reg2-specified register.                                                                                              |

| ANDBSU      | _                 | II     | -  | _  | _ | - | Transfer after ANDing bit strings:<br>Performs a logical AND operation on a source b<br>string and a destination bit string, then transfers th<br>result to the destination bit string.                                                                                                                  |

| ANDI        | imm16, reg1, reg2 | V      | _  | 0  | 0 | * | AND:<br>Sign-extends the 16-bit immediate data to 32 bits, and<br>performs a logical AND operation on the extended<br>immediate data and the word data in the reg1-specified<br>register, then stores the result into the reg2-specified<br>register.                                                    |

| ANDNBSU     | _                 | ΙΙ     | -  | _  | - | - | Transfer after NOTting a bit string then ANDing it with<br>another bit string:<br>Performs a logical AND operation on a destination b<br>string and the 1's complement of a source bit string<br>then transfers the result to the destination bit string                                                 |

| BC          | disp9             | 111    | -  | -  | - | - | Conditional branch (if Carry):<br>PC relative branch                                                                                                                                                                                                                                                     |

| BE          | disp9             | III    | -  | -  | - | - | Conditional branch (if Equal):<br>PC relative branch                                                                                                                                                                                                                                                     |

| BGE         | disp9             | III    | -  | -  | - | - | Conditional branch (if Greater than or Equal):<br>PC relative branch                                                                                                                                                                                                                                     |

| BGT         | disp9             | III    | -  | -  | - | - | Conditional branch (if Greater than):<br>PC relative branch                                                                                                                                                                                                                                              |

# Table 9-1. Instruction Mnemonics (in alphabetical order) (1/9)

| Instruction | Operand (s)         | Format | CY ( | VC | S | Ζ | Instruction Function                                                                                                                                                                                                             |

|-------------|---------------------|--------|------|----|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic    |                     |        |      |    |   |   |                                                                                                                                                                                                                                  |

| BH          | disp9               | 111    | -    | -  | - | - | Conditional branch (if Higher):<br>PC relative branch                                                                                                                                                                            |

| BL          | disp9               | III    | -    | -  | - | - | Conditional branch (if Lower):<br>PC relative branch                                                                                                                                                                             |

| BLE         | disp9               | Ш      | -    | -  | - | - | Conditional branch (if Less than or Equal):<br>PC relative branch                                                                                                                                                                |

| BLT         | disp9               | III    | -    | -  | - | - | Conditional branch (if Less than):<br>PC relative branch                                                                                                                                                                         |

| BN          | disp9               | Ш      | -    | -  | - | - | Conditional branch (if Negative):<br>PC relative branch                                                                                                                                                                          |

| BNC         | disp9               | 111    | -    | -  | - | - | Conditional branch (if Not Carry):<br>PC relative branch                                                                                                                                                                         |

| BNE         | disp9               | 111    | -    | -  | - | - | Conditional branch (if Not Equal):<br>PC relative branch                                                                                                                                                                         |

| BNH         | disp9               | Ш      | -    | -  | - | - | Conditional branch (if Not Higher):<br>PC relative branch                                                                                                                                                                        |

| BNL         | disp9               | Ш      | -    | -  | - | - | Conditional branch (if Not Lower):<br>PC relative branch                                                                                                                                                                         |

| BNV         | disp9               | Ш      | -    | -  | - | - | Conditional branch (if Not Overflow):<br>PC relative branch                                                                                                                                                                      |

| BNZ         | disp9               | Ш      | -    | -  | - | - | Conditional branch (if Not Zero):<br>PC relative branch                                                                                                                                                                          |

| BP          | disp9               | 111    | -    | -  | - | - | Conditional branch (if Positive):<br>PC relative branch                                                                                                                                                                          |

| BR          | disp9               | 111    | -    | -  | - | - | Unconditional branch:<br>PC relative branch                                                                                                                                                                                      |

| BV          | disp9               | Ш      | -    | -  | - | - | Conditional branch (if Overflow):<br>PC relative branch                                                                                                                                                                          |

| BZ          | disp9               | 111    | -    | -  | - | - | Conditional branch (if Zero):<br>PC relative branch                                                                                                                                                                              |

| CAXI        | disp16 [reg1], reg2 | VI     | *    | *  | * | * | Inter-processor synchronization in a multi-processor system.                                                                                                                                                                     |

| СМР         | reg1, reg2          | I      | *    | *  | * | * | Comparison:<br>Subtracts the word data in the reg1-specified register<br>from that for reg2 for comparison, then changes flags<br>according to the result.                                                                       |

| СМР         | imm5, reg2          | II     | *    | *  | * | * | Comparison:<br>Sign-extends the 5-bit immediate data to 32 bits, and<br>subtracts the extended immediate data from the word<br>data in the reg2-specified register for comparison<br>then changes flags according to the result. |

| CMPF.S      | reg1, reg2          | VII    | *    | 0  | * | * | Floating-point comparison:<br>Subtracts the single-precision floating-point data in<br>the reg1-specified register from that for reg2 for<br>comparison, then changes flags according to the<br>result.                          |

# Table 9-1. Instruction Mnemonics (in alphabetical order) (2/9)

| Instruction        | Operand (s)         | Format | CY | OV | S | Z | Instruction Function                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|---------------------|--------|----|----|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic<br>CVT.SW | reg1, reg2          | VII    | -  | 0  | * | * | Data conversion from floating-point to integer:<br>Converts the single-precision floating-point data in the<br>reg1-specified register into an integer data, then stores<br>the result into the reg2-specified register while changing<br>flags according to the result.                                                                                                       |

| CVT.WS             | reg1, reg2          | VII    | *  | 0  | * | * | Data conversion from integer to floating-point:<br>Converts the integer data in the reg1-specified register<br>into a single-precision floating-point data, then stores<br>the result into the reg2-specified register while changing<br>flags according to the result.                                                                                                        |

| DIV                | reg1, reg2          | I      | _  | *  | * | * | Signed division:<br>Divides the word data in the reg2-specified register by<br>that for reg1 with their sign bits validated, then stores<br>the quotient into the reg2-specified register and the<br>remainder into r30. Division is performed so that the<br>sign of the remainder matches that of the dividend.                                                              |

| DIVF.S             | reg1, reg2          | VII    | *  | 0  | * | * | Floating-point division:<br>Divides the single-precision floating-point data in the<br>reg2-specified register by that for reg1, then stores the<br>result into the reg2-specified register while changing<br>flags according to the result.                                                                                                                                   |

| DIVU               | reg1, reg2          | I      | _  | 0  | * | * | Unsigned division:<br>Divides the word data in the reg2-specified register by<br>that for reg1 with their data handled as unsigned data<br>then stores the quotient into the reg2-specified registe<br>and the remainder into r30. Division is performed so<br>that the sign of the remainder matches that of the<br>dividend.                                                 |

| HALT               | -                   | П      | -  | -  | - | - | Processor stop                                                                                                                                                                                                                                                                                                                                                                 |

| IN.B               | disp16 [reg1], reg2 | VI     | _  | _  | _ | - | Port input:<br>Sign-extends the 16-bit displacement to 32 bits, and<br>adds the extended displacement and the content of<br>the reg1-specified register to generate a 32-bit unsigned<br>port address, then reads the byte data located at the<br>generated port address, zero-extends the byte data to<br>32 bits, and stores the result into the reg2-specified<br>register. |

| IN.H               | disp16 [reg1], reg2 | VI     | _  | -  | _ | _ | Port input:<br>Sign-extends the 16-bit displacement to 32 bits, and<br>adds the extended displacement and the content of<br>the reg1-specified register to generate a 32-bit unsigned<br>port address, then reads the halfword data located a<br>the generated port address while masking the address's<br>bit 0 to 0, zero-extends the halfword data to 32 bits               |

and stores the result into the reg2-specified register.

# Table 9-1. Instruction Mnemonics (in alphabetical order) (3/9)

| Instruction | Operand (s)         | Format | CY O | V | S | Ζ | Instruction Function                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|---------------------|--------|------|---|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic    |                     |        |      |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                |

| IN.W        | disp16 [reg1], reg2 | VI     |      | _ | _ | - | Port input:<br>Sign-extends the 16-bit displacement to 32 bits, and<br>adds the extended displacement and the content of<br>the reg1-specified register to generate a 32-bit unsigned<br>port address, then reads the word data located at the<br>generated address while masking the address's bits<br>0 and 1 to 0, and stores the word into the reg2-<br>specified register.                |

| JAL         | disp26              | IV     |      | _ | _ | _ | Jump and link:<br>Increments the current PC by 4, then saves it into r31,<br>and sign-extends the 26-bit displacement to 32 bits<br>while masking the displacement's bit 0 to 0, adds the<br>extended displacement and the PC value, loads the<br>PC with the addition result, so that the instruction<br>stored at the PC-pointing address is executed next.                                  |

| JMP         | [reg1]              | I      |      | _ | - | _ | Register-indirect unconditional branch:<br>Loads the PC with the jump address value in the reg1-<br>specified register while masking the value's bit 0 to 0,<br>so that the instruction stored at the address pointed<br>by the reg1-specified register is executed next.                                                                                                                      |

| JR          | disp26              | IV     |      | _ | _ | _ | Unconditional branch:<br>Sign-extends the 26-bit displacement to 32 bits while<br>masking bit 0 to 0, adds the result with the current PC<br>value, and loads the PC with the addition result so that<br>the instruction stored at the PC-pointing address is<br>executed next.                                                                                                                |

| LD.B        | disp16 [reg1], reg2 | VI     |      | _ | _ | _ | Byte load:<br>Sign-extends the 16-bit displacement to 32 bits, and<br>adds the result with the content of the reg1-specified<br>register to generate the 32-bit unsigned address, ther<br>reads the byte data located at the generated address<br>sign-extends the byte data to 32 bits, and stores the<br>result into the reg2-specified register.                                            |

| LD.H        | disp16 [reg1], reg2 | VI     |      | _ | _ | - | Halfword load:<br>Sign-extends the 16-bit displacement to 32 bits, and<br>adds the result with the content of the reg1-specified<br>register to generate a 32-bit unsigned address while<br>masking its bit 0 to 0, then reads the halfword data<br>located at the generated address, sign-extends the<br>halfword data to 32 bits, and stores the result into the<br>reg2-specified register. |

| LD.W        | disp16 [reg1], reg2 | VI     |      | _ | - | - | Word load:<br>Sign-extends the 16-bit displacement to 32 bits and<br>adds the result with the content of the reg1-specified<br>register to generate a 32-bit unsigned address while<br>masking bits 0 and 1 to 0, then reads the word data<br>located at the generated address and stores the data<br>into the reg2-specified register.                                                        |

# Table 9-1. Instruction Mnemonics (in alphabetical order) (4/9)

| Instruction | Operand (s)       | Format | CY | OV | S | Z | Instruction Function                                                                                                                                                                                                                                                                                                           |

|-------------|-------------------|--------|----|----|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic    |                   |        |    |    |   |   |                                                                                                                                                                                                                                                                                                                                |

| LDSR        | reg2, regID       | II     | *  | *  | * | * | Loading system register:<br>Transfers the word data in the reg2-specified registe<br>to the system register specified with the system registe<br>number (regID).                                                                                                                                                               |

| MOV         | reg1, reg2        | I      | -  | -  | - | - | Transferring data:<br>Loads the reg2-specified register with the word dat<br>in of the reg1-specified register.                                                                                                                                                                                                                |